功放设计

功放基础理论

设计指标

增益:

实际增益

资用功率增益:

a可以理解为晶体管

输出功率

功率效率和功率附加效率

功率效率:

是指输出功率Pout和直流信号源提供的直流功率Pdc相比得到的数值,表征的是放大器将信号源提供的功率转换成射频输出功率的能力。

功率附加效率:

针对于晶体管

线性度

1dB压缩点

三阶交调点

临近信道功率比

稳定性

稳定性优化方法:

1 栅极源级电路设计

2 改变匹配电路,增加反馈回路,降低电路闭环增益

S参数

S11 S22反应对应端口的匹配,要求S11 S22<-10dB

S21 反应输出功率与输入功率的比值,放大:增益;减小:插入损耗

S12:反向隔离程度

最大资用增益MAG:是共轭匹配下晶体管所能获得的最大增益

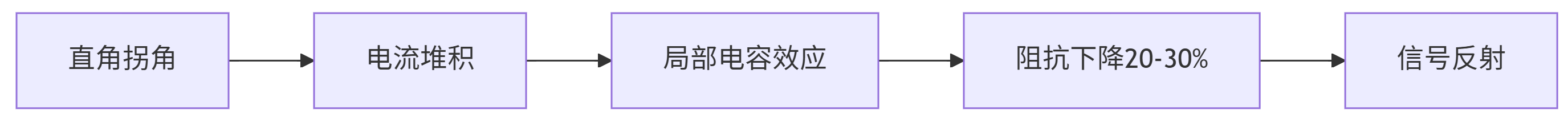

匹配技术

匹配要求的就是要让射频信号以功率最大化传输

双元件匹配

L型匹配

并联原件改善负载阻抗,使得负载是不与源阻抗相等。

虚部和串联电抗抵消。

复负载匹配设计

谐振匹配法

使用等值异号的电抗元件和寄生电抗组成谐振电路

1通过谐振抵消负载的电抗部分(如果负载电抗为并联LC元件,则消耗元件也是并联的CL元件)

2使用L型匹配理论设计LC双元件匹配电路(设计过程不考虑已经消耗的LC负载元件)

3最终的匹配电路进行串并联合并

先消除虚部,例如负载有并联的电容,我们通过并联一个电感实现LC谐振,这样就能将负载阻抗的虚部抵消。

吸收匹配法

使用匹配网络吸收电抗成分

三元件匹配

相对于双元件网络:拥有更灵活的Q值和更灵活的带宽设计

π型网络和T型网络,需要确定Q值

Smith圆图匹配

参数归一化

反射系数作为基底

反射系数为系统不变量

窄带匹配

Smith圆图轨迹和分立元件连接关系

等电阻圆顺时针串电感,等电阻圆逆时针串电容

等电导圆顺时针并联电容,等电导圆逆时针并联电感

做窄带匹配通常采用L型、π型和T型匹配网络

串联电感沿着等电阻圆顺时针旋转,轨迹长度越长,值越大

串联电容沿着等电阻圆逆时针旋转,轨迹长度越长,值越小

并联电感沿着等电导圆逆时针旋转,轨迹长度越长,值越小

并联电容沿着等电导圆顺时针旋转,轨迹长度越长,值越大

π型匹配

L型匹配电路只有两个元件,元件值随着网络拓扑的选定而固定。(一个电感L,一个电容C的组合,通过引入适当的电抗(+jXL 和 -jXC),抵消掉负载阻抗中的虚部(jX),并最终在匹配点将整个网络呈现的阻抗变换到源阻抗的共轭值(以实现最大功率传输)。目的是抵消虚部,所以是固定的)

π型匹配电路有三个元件,元件值不固定,有无穷多种组合,不同组合的Q值也不同,有助于提升带宽。

T型匹配

和π型网络类似

宽带匹配思想

宽频一般指相对带宽>10%

注:

绝对带宽:这是最简单、最直观的带宽概念。它指的是一个系统能够有效工作的频率范围宽度。它的单位是Hz。

相对带宽:这个概念的引入是为了衡量带宽相对于其中心频率的比例或百分比。它描述的是带宽的“宽窄程度”与系统工作中心位置的关系。这是一个无量纲的量,通常用百分比 (%) 或小数表示。

窄带系统 : 相对带宽通常 < 1%

宽带匹配的本质就是使得在较宽的频带内,满足回波损耗(S11<-10dB)或者驻波比的要求,在smith圆图中要求所有的频带内的S11轨道都要移动到VSWR=2,等电压驻波比圆中。

将VSWR=2的圆内部的阻抗轨迹的长度变长,即可实现带宽拓展。

注:VSWR(电压驻波比)与匹配关系:

VSWR=2 对应 反射系数 |Γ|=0.333

- 物理意义:当端口反射能量≤11.1%(|Γ|²≈0.111)时视为“良好匹配”,是工程常用标准。

- Smith圆图表现:VSWR=2的圆是圆心在(50Ω,0)、半径|Γ|=1/3的圆

- 圆内区域:|Γ|<1/3,VSWR<2,匹配良好。

| 类型 | 特点 | 适用场景 |

|---|---|---|

| 多节λ/4阶梯 | 阻抗渐变,带宽可控 | 高频PCB/微带线 |

| π/T型网络 | 紧凑,可调参数多 | 集成电路/低频 |

| 混合耦合器 | 超宽带,但尺寸大 | 基站/雷达 |

谐振宽带匹配

设计要求:设计宽带匹配电路时,需要保持原始中心频点的工作频点不变,只需要折叠带宽的上下频点即可;

所以我们需要并联LC谐振网络,保证中心频率不发生变化。

并联LC谐振器适用于开口向右的圆图

串联LC谐振器适用于开口向左的圆图

Snp模型与设计

Snp模型

是线性S参数文件(或者是Z、Y、H、G参数等),n表示端口数。当n=2时可以包含噪声参数。

生成SnP文件有三种方法

1.手动编辑文本文件;

2.基于HFSS、ADS、AWR等仿真数据导出;

3.基于网络分析仪测试数据导出

SnP格式

抬头 # freq_units parameter format Rn

#告诉编译器随后的符号是关于参数的

freq_units设置单位,Hz等

parameter是设置参数:

S1P器件可以设置S.Y.Z参数

S2P器件可以设置SYZH参数

S3P和S4P可以设置S参数

format 是内容格式

dB、MA(幅度角度)、RI(实部虚部)(格式来表示)

Rn是阻抗设置,一般为50欧姆

若无#开始标志,则采用默认,!表示S2P的注释

例:频率单位为GHz,S参数,用实部-虚部表示,归一化到100欧姆

例:# GHz S RI R 100

基于S2P文件,实现50W功率放大器

S21代表我们的增益

通过看Smith圆图的S11和S22可以看到其阻抗值

在阻抗圆图上看中心频率f0处的值,中心频率就是频率范围的中间

S11为输入口阻值,S22为输出口阻值

双击m1和m2的文本框可以改参数,将format里面阻值z0是normalized,改为50,就是乘以50,进行反归一化

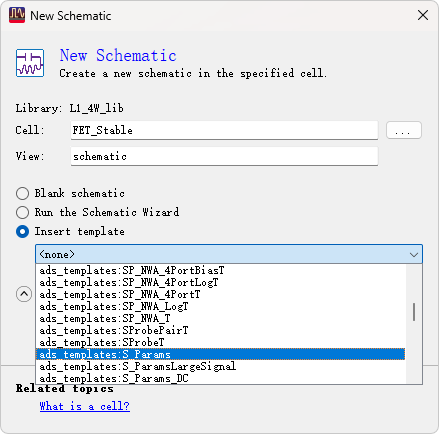

第一步,先建立FET_Stable测试S参数

首先是导入S参数仿真模型

再将Sp文件导入(在Data Items 中,上面标注为S,图标为四个pin的贴片样式,写着N)

连接好线进行仿真

然后先看S11,S22,S21的dB图

然后通过smith圆图来看S11和S22对应于输入阻抗和输出阻抗的值

当然,在标记好m1和m2之后,将频率f设为中心频率。

然后去归一化,得到源阻抗

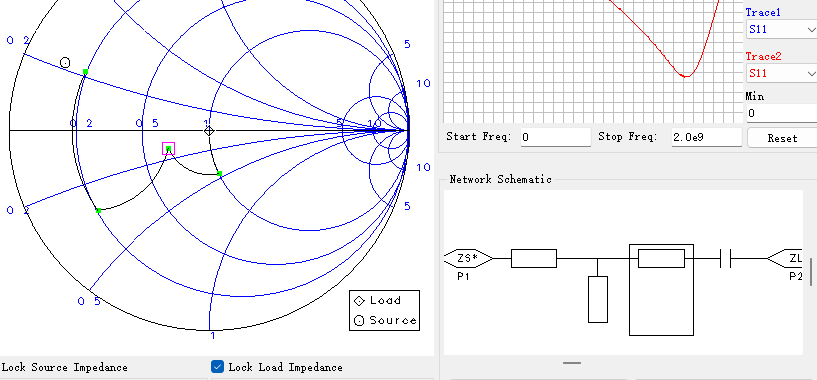

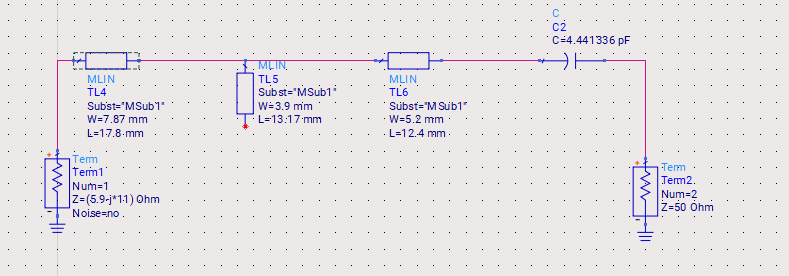

第二步,进行输出阻抗匹配

建立Match文件(in 和out)

先看out match

也是新建s参数仿真模型,然后给Term1设置为S22去归一化的值,要将输出匹配到50欧姆,所以是将Term2设置为50

加入Smith圆图

smith圆图配置:

Fp为中心频率

Source Type = Complex Impedance //源类型=复数阻抗

SourceEnable = True //使能

Zg= 输出阻抗(记得带单位)

负载部分也需要改

LoadType设置为Res

使能也打开

RL改为50ohm

在LoadImpType = Output Imp

之后在Tools里面选择Simth Chat

进去之后选第二项,从两端更新到Smith

注意

在15w以上的匹配最好都用微带线进行匹配,不要用RLC

功率耐受性:微带线是“铜墙铁壁”,RLC是“瓷器店”

高频稳定性:微带线是“高速公路”,RLC是“石子路”

损耗控制:微带线“省油”,RLC“费油”

热管理:微带线是“散热片”,RLC是“保温杯”

第三步,进行SmithChat匹配

我们是从50欧姆往回匹配

首先将频率改为中心频率,阻抗50,勾选归一化

然后先串联一个电容(既作匹配又作隔直)

做微带线匹配时,首先应该先考虑管子的大小,焊盘的大小。微带线不能比焊盘还小吧,这样焊接不上还容易失配。最近在设计16w功放的PCB的时候也是体会到了,根据厂家来的那些管子的填充不是随意的,是微带线!

然后先串联一个微带线,再并联一个微带线,再串一个即可

微带线阻抗越低,角度越小,在PCB上的宽度越宽

做好之后,保存导入。再进行仿真

看S11和S12

S11就是反射系数,要求小于-10dB,S12代表插损值,DS说要小于-20dB

不是到这里就结束了

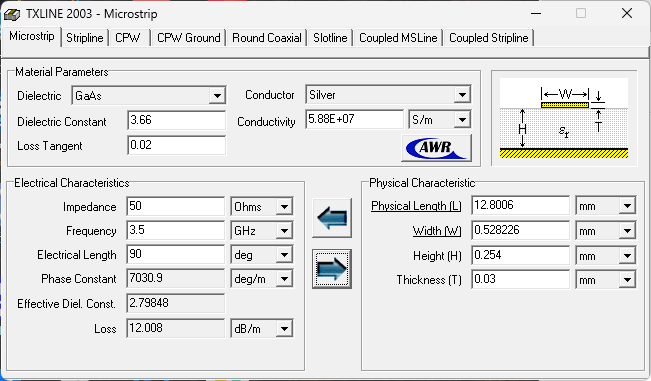

这里微带线是理想的微带线,还要转化为实际微带线

电长度讲解

光速 / 频率=波长

波长为1,对应360°电角度

在库里面找到TLines,找到MSUB(第一个)控件,叫做微带线基板

基板宽度H=0.76mm,介电常数(FR4)=3.66,铜厚Hu不管,板厚T=0.03mm,损耗角正切值TanD=0.0037,其他不设置

然后用实际的微带线来代替,实际的微带线也在这里叫MLIN,注意电容按照原来的复制粘贴上去即可

通过计算软件来实际计算每个微带线的宽度和电长度

仿真得到与原仿真一致的曲线之后,需要将微带线连接进行优化。

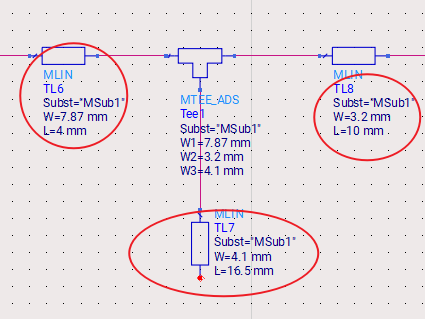

可以用三端口进行连接(MTEE)

注意,这里引入三端口连接的微带线,会导致我们S11的谐振频率向左偏移,正常现象

需要修改其他位置

思考一下,如果三端口左边是宽8.3mm,右边宽2.8mm,下面并联的宽2.3mm

那我们从左边看过去,是不是相当于L增加了2.3mm

所以我们减掉即可,将三个端口都减一点,偏到大于等于2.4G即可,因为后续还要再加偏置

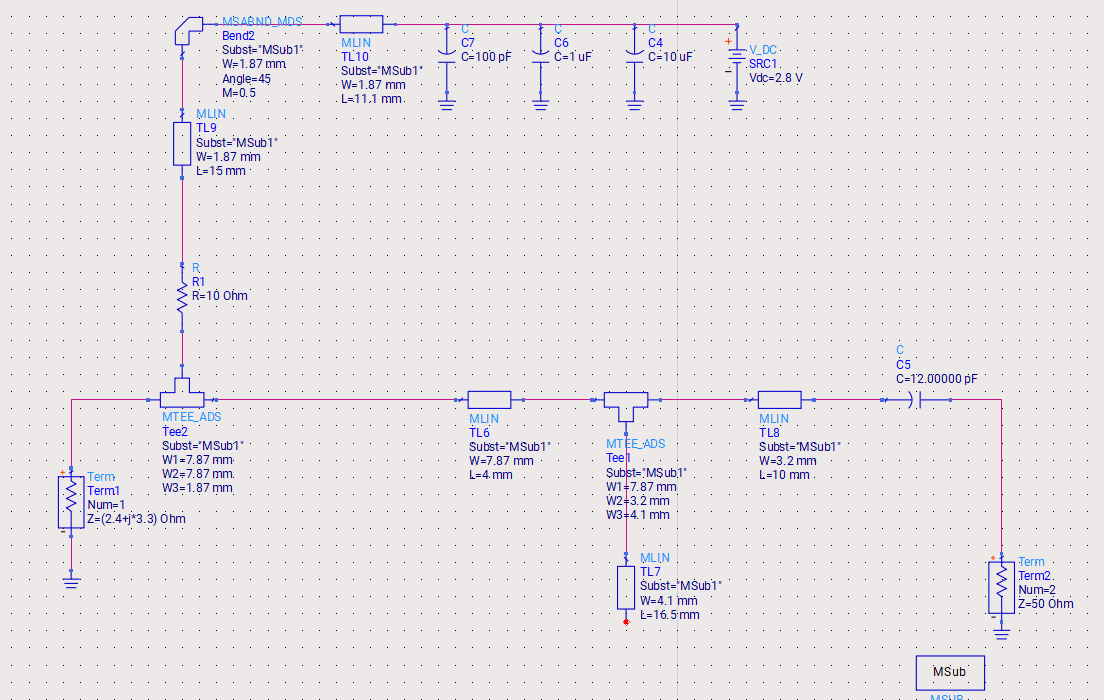

这里我们需要加偏置

在输入口Term1处加入四分之一波长微带线,这里阻值设置为50Ω,电角度为90,算出实际波长

这里加入三分端口,宽度和左右相同(等于右边微带线宽度),而并联的那个口则是宽度选择为刚刚计算出来的宽度

第三端口为刚刚的宽度,在第三端口再加入微带线TL7,宽度不变,长度看之间计算的长度,这里一般采用两节,所以看情况拆一下即可

第一节加入之后,第二节加一个拐角(MSABND),其W保持不变和TL7一致

作用是:消除阻抗突变

这里我们计算出来四分之一波长的长度之后,减去TL7,剩下的就是我们最后加的部分TL8,宽度不变

最后加三个个电容,防止信号泄漏,大小100pf、1uf、10uf

最后加入电压源Vcc(S2p参数可查,这边是28v)

之后进行仿真,可能频率任然会偏,这里给中间三端口并联的微带线再调低一点

第四步,进行输入匹配

打开inmatch

首先是建立S参数仿真,对于输入阻抗是1.13+j*4.28

输入Term1给50Ω不变,输出给1.13+j*4.28

插入史密斯圆图,设置参数

先设置一下频率,再设置源阻抗类型

Term2设置为负阻抗,这里的ZL设置为其共轭阻抗1.13-j*4.28,设置为输出阻抗

注意,这里是匹配到50欧姆,同时呢还是要保证这个第一级微带线足够的宽

所以先串联一个微带线,再通过串电容绕回来,微带线设置为10欧姆,改变电长度找等阻抗圆再转回来

电容容值拉回到中心50欧姆

一个电容电感即可

之后添加Msub,从输出端copy即可,保证参数一致

再加一个微带线和一个电容(实际微带线)

计算得到电容为W=13.2,L为11.4

然后还是需要将输出端的偏置部分留出偏置区

最简单的方法就是输出端的偏置直接复制过来

也是接一个三端口Tee2,再接TL7,再接转角,再接TL8,再接三个电容,再接电源(这里是-2.9)。整体做一个Y轴镜像即可

注意,此时三端口宽度改左端口即可

仿真一下微调一下即可

第五步,将输入输出部分全部搬到第一个图里头

进行整体验证,仿真

看S21,也就是增益,在目标频率时是否符合我们的要求

再看反射系数和驻波比

若S22较差,微调一下。

调整OUT部分,在4分之一波长微带线三端口之后的第二个三端口连接的部分

TL4和TL5,接近电容的TL6不用管。

点击仿真右边那个调写,弹出窗口不管,点击我们要调的TL4

选择L,然后多点几个,给TL5,TL6都选上,然后打开仿真和微调窗口

可以边调边看

可以改step然后调好了点击更新即可

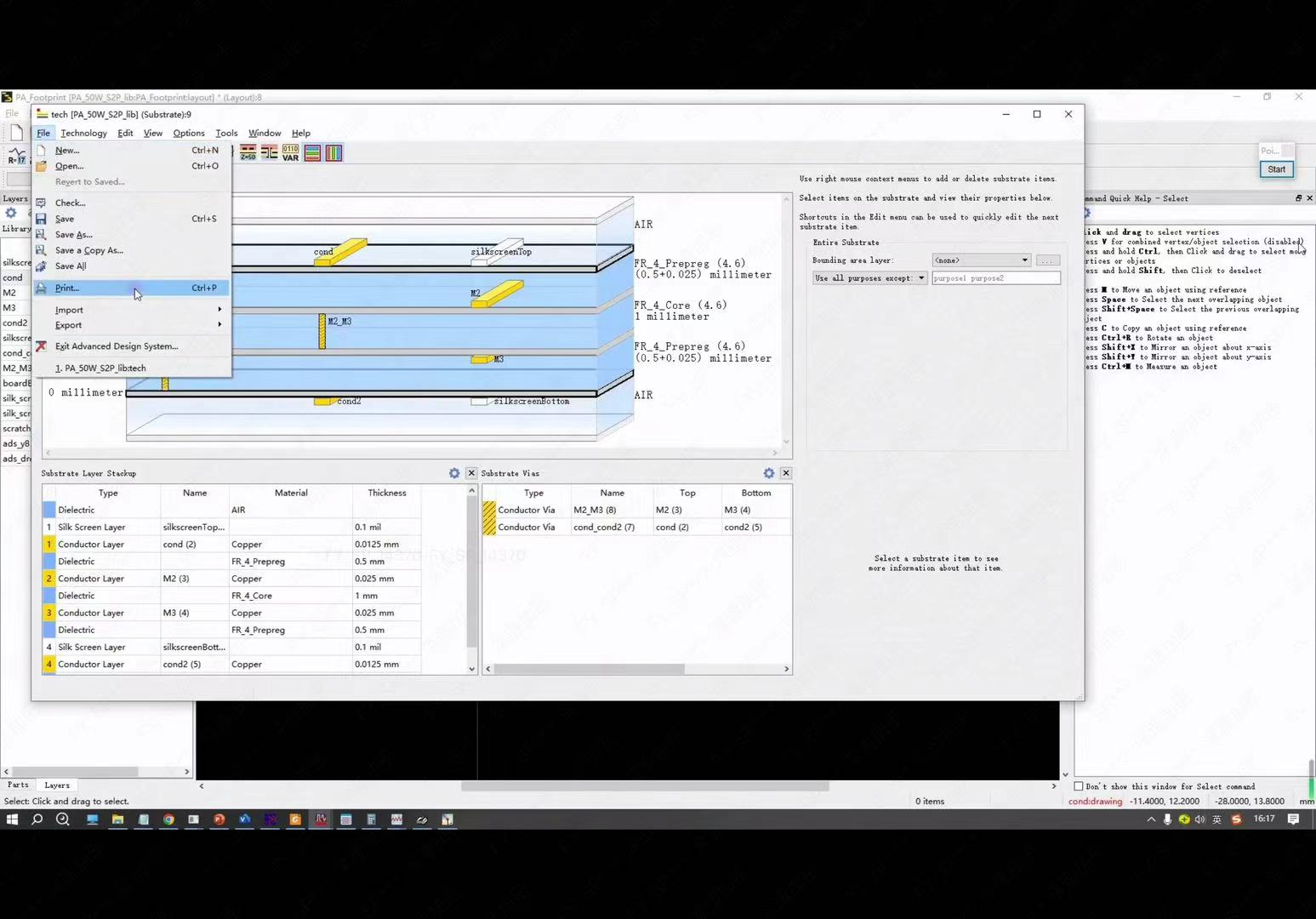

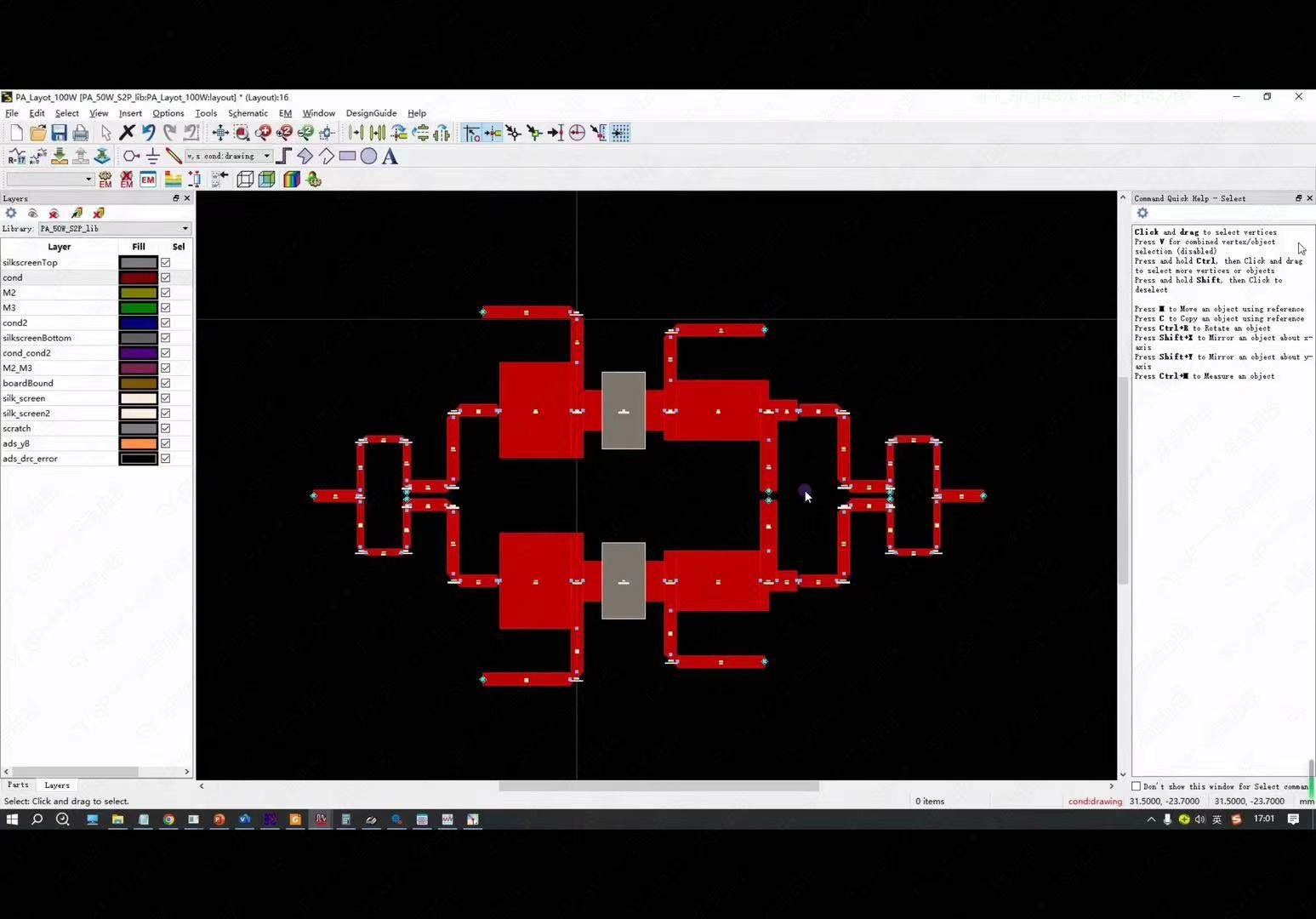

第六步,建立LayOut

在输入电容前面再加一个微带线,输出端也加一个,因为是50Ω,所以不影响匹配,L改为5mm,仿真一下确认无问题

复制所有东西,再新建一个文件夹LayOut

建立PA_LayOut文件

然后粘贴我们的文件

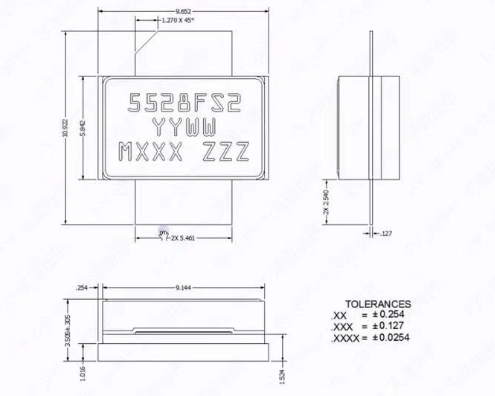

这里我们的三极管是Sp文件,这里我们需要新建一个封装

在这个文件夹,新建一个lib文件

PA_Footprint

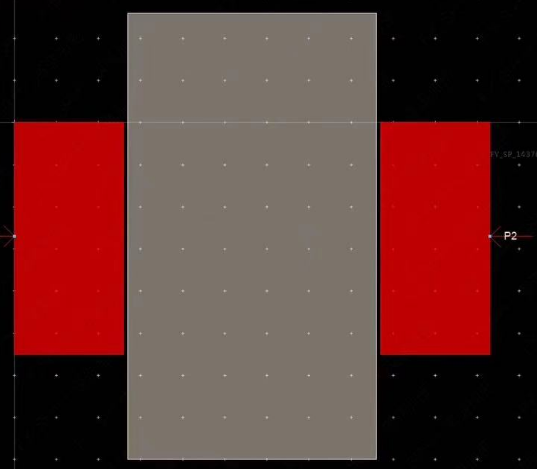

对着手册来建立,首先画焊盘,切到cond(金属层)层

然后直接开画,dx=2.6,dy=5.5

和AD自己画封转库即可

两个焊盘画好了,切到Silk层,画丝印

画到中间即可,切到cond层

添加两个端口,在GND左边的那个

要焊接到里面,所以pin要接到两个焊盘靠近丝印的部分(注:这里是错误的,会在后面加上新图)

(第六步回来看)整错了不要紧,直接画成这样的,然后再点击EM,再点击EM,点击Component,选第一个create,点OK点yes,再点yes,再点ok

然后再加叠层,(左上角三个EM标识的右边,也就是第四个)

点击new,greate即可

再点Import导入,最下面Substrate From Schematic,选择PA_Layout,点击schematic

删除cond2

点击保存,全关了

点击菜单选项EM,第二个Simulation Settings

create

调整介质基板,点击第三个Substrate,选第1个PA_50w_S2p_lib:PA_Layout

保存其他的不用管

再点击EM,点击Component,选第一个create,点击几次ok即可

再回到Layout原理图之中

去除S2p文件,屏蔽(第二个屏蔽)

点击Parts下面的那个,时钟右边那个柱状图一样的图标,也就是我们的library

在第一个WorkSpace里面的,PA_Footprint,可以直接导入我们的封装,连接

四分之一波长微带线的偏置部分的电容屏蔽掉

Term1和Term2以及S参数设计那个大的也屏蔽

再给所有电容换成带封装的(未屏蔽的电容,也就是我们做匹配的电容),点击库,选择Lumped-With ArtWork,选择电容PAD1(0805封装)

网上查一下0805的封装,改PAD1的W,L1,这里的S指的是两个焊盘之间的间距

这里W=1.2mm,S=0.4mm,L1=2mm,再改电容值

第七步,创建封装

点击Layout,点击create

点Apply

这里手动调了一下,说明他有问题

看上述封装调整部分

更新之后重新连接

再重新从第六步一开始操作

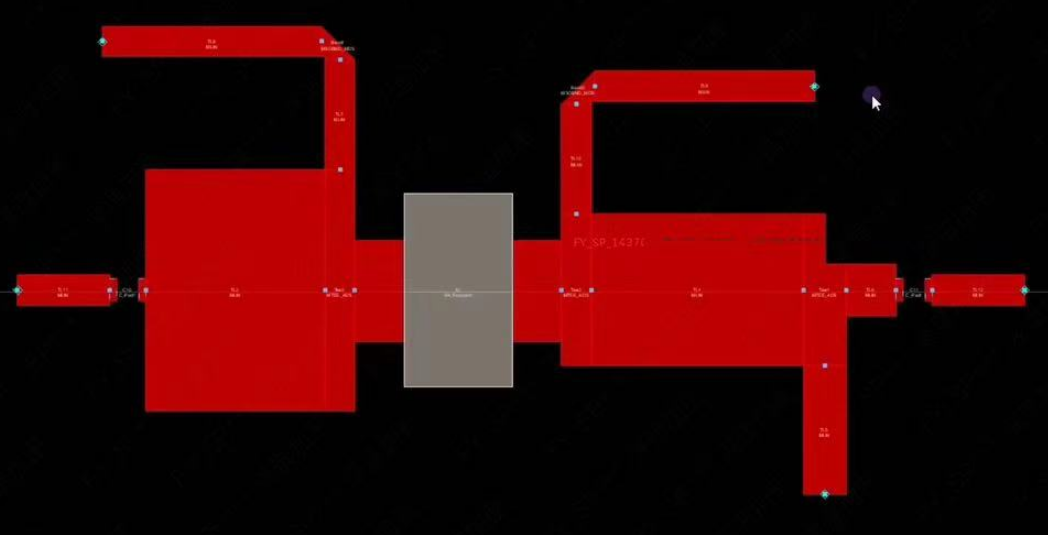

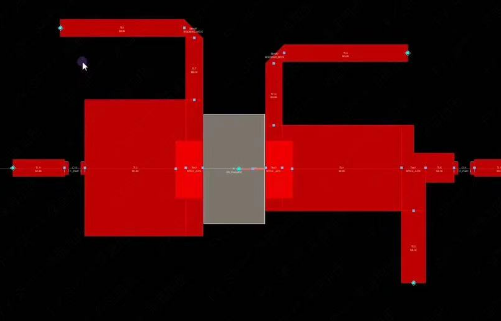

得到最新的版图

但是我们实际焊接的时候,是需要将焊盘压上去的

所以手动挪一下

这里就可以导出到AD中即可

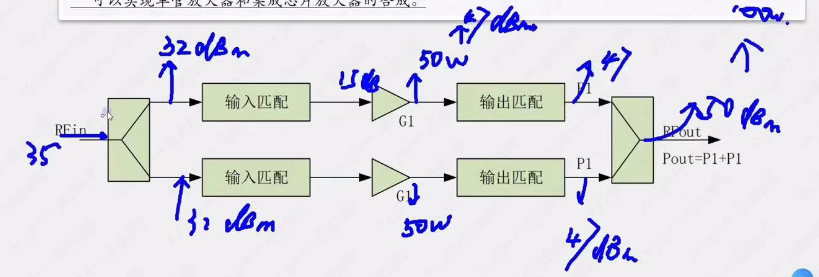

100W功率合成放大器设计

合成技术

合成技术

本质是将两个或者两个以上的单管功放输出功率进行同相相加,实现功率的倍数叠加

合路器方案

威尔金森功分器 / 3dB电桥 / 桥式反相器

放大器方案

可以实现单管放大器和集成芯片放大器的合成

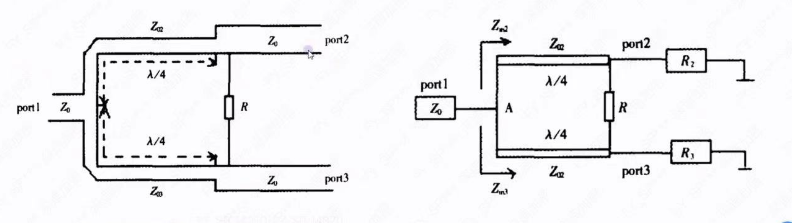

威尔金森功分器

属于混合型功分器,在普通功分器的输出端口之间引入隔离电阻,实现链路的匹配和隔离

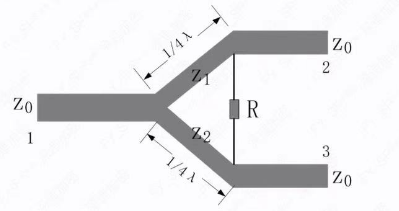

一分二等分威尔金森功分器

1为信号输入端口,2和3为信号输出端口。所有端口负载均为Z0

Z1=Z2=根号二Z0,R=2Z0

设计要求:

输入和输出端口之间需要完全匹配

输出端口需要实现隔离,工作频段内的隔离度<-20dB

频段内VSWR<1.3

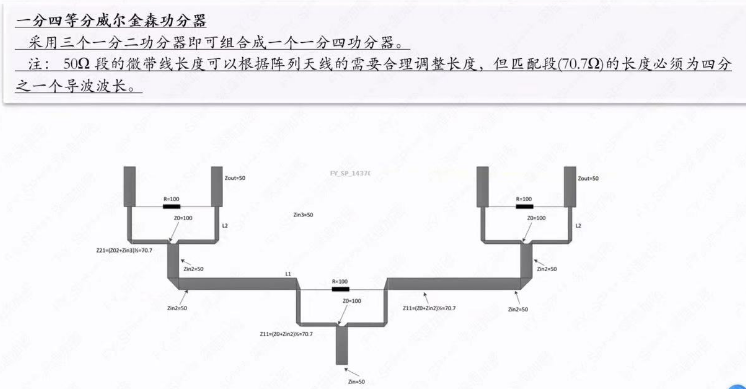

还有1分四

基于上面50w级S波段放大器设计最大输出功率不低于100w的功率放大器,要求实现(Psat>100w,VSWR<2)

第一步回到上面工程

新建 new folder,100w_PA

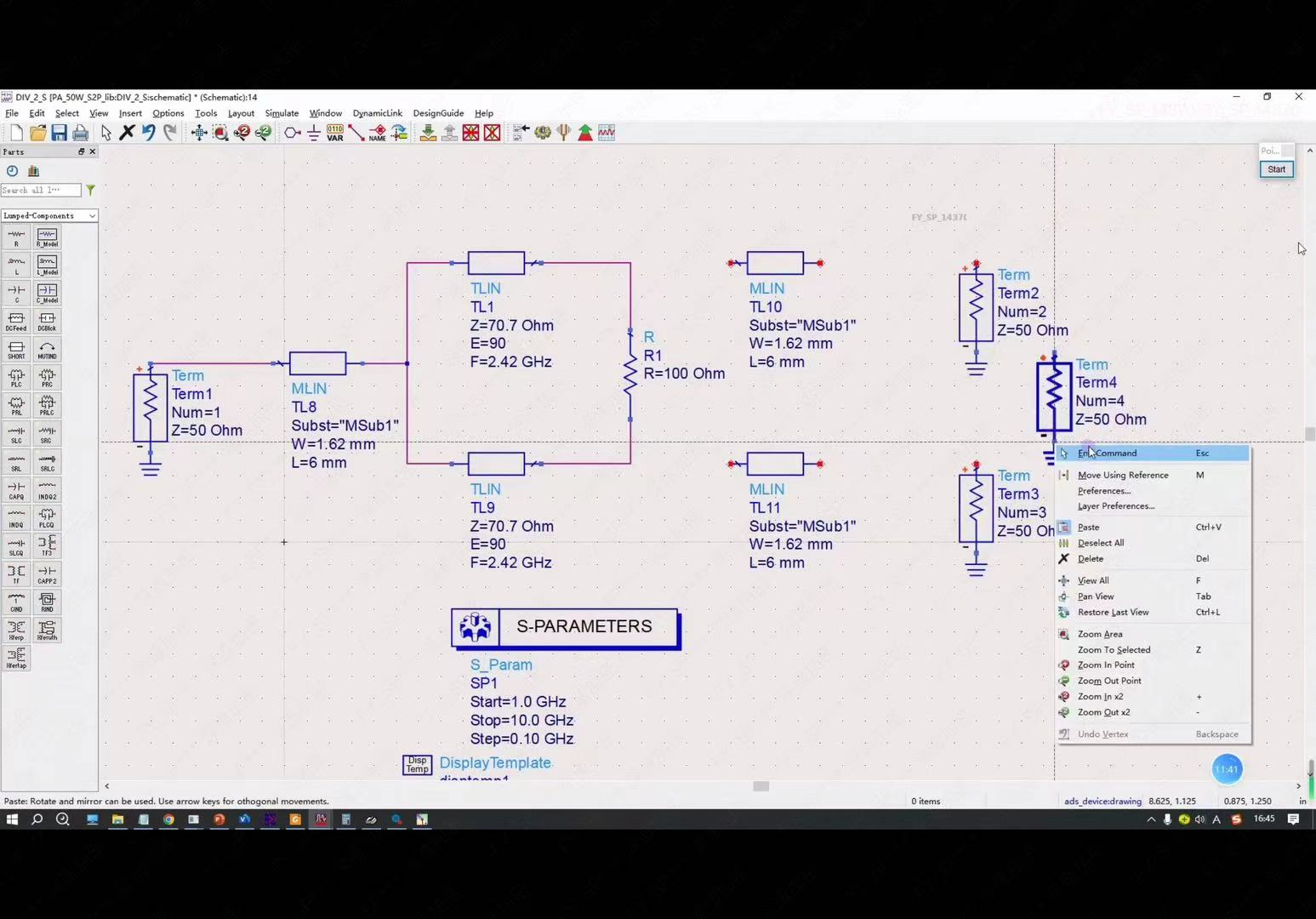

新建DIV_2_S,导入S参数

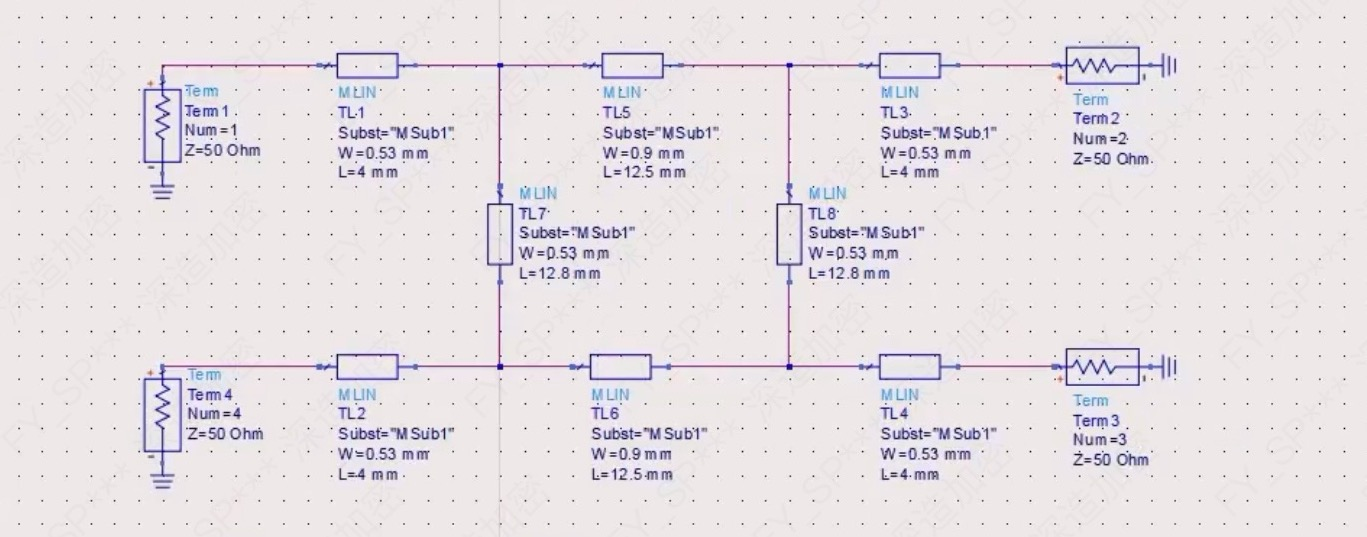

切到理想微带,复制一个MLIN和新建一个TLIN,复制成两个TLIN

再接一个电阻,构成1分2功分器

分别接两个端口

再加入微带线基板

仿真查看S11、S22、S33

再看S12和S13(少了多少)

比如输入10w,输出为两个5w,相当于少了一半,刚好是3dB

然后再将仿真微带线换成实际微带线

之后在中间接上三分微带线

再加倒角

再加一段微带线,再加倒角,在加一段,再加一个三分口接上

大概计算一下长度,和通过ADS计算的长度差不多就行,倒角不用算长度

理想电容也得改

第二步,将之前做的功放全部整过来

将源工程复制过来,复制两个,将功分器两个端口分别接输入端

将功分器也复制一份,镜像之后接在功放输出端

第三步,做版图

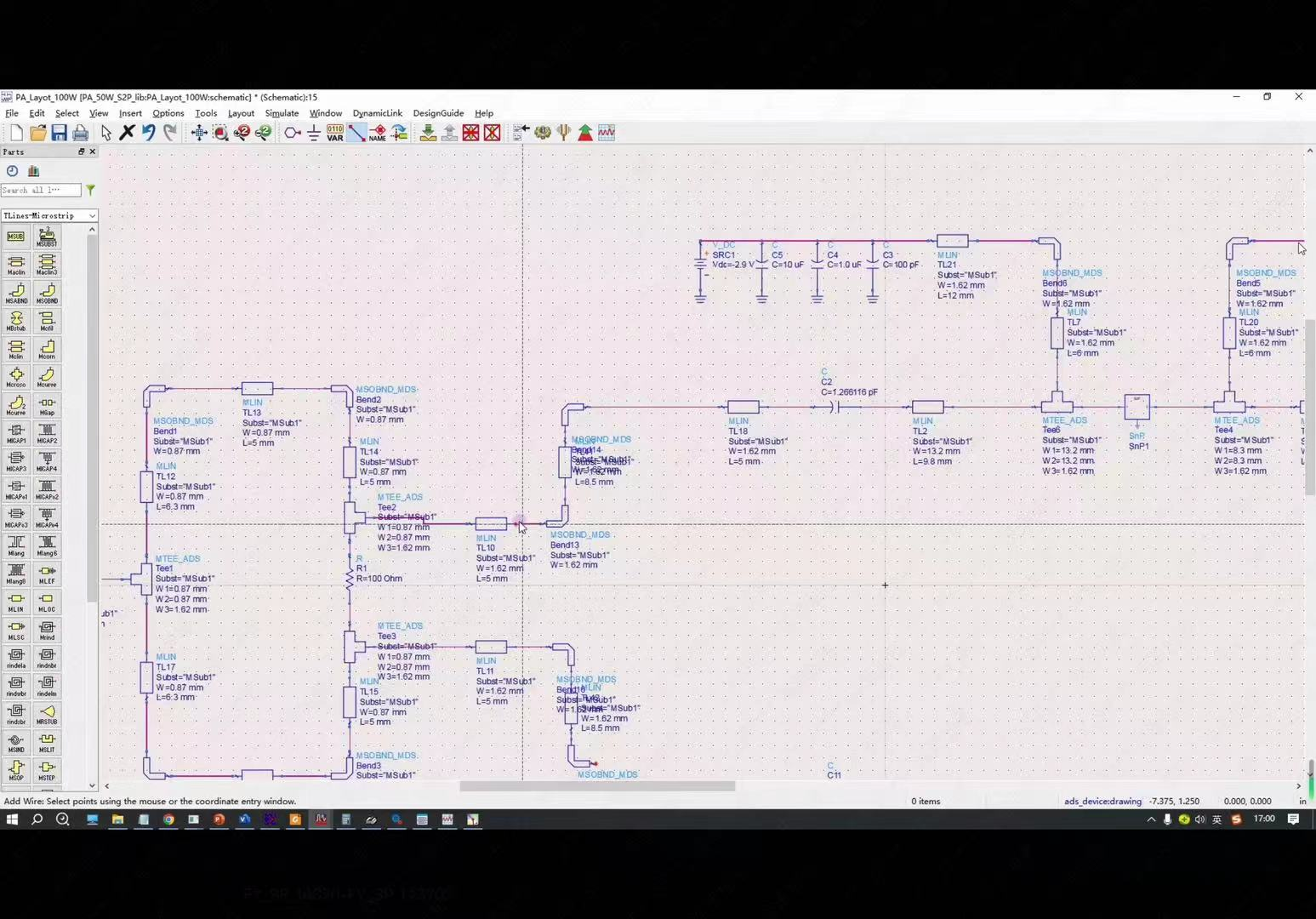

新建Schematic,PA_Layout_100w

将整个电路复制过来,务必将整个电路关于x轴镜像对称

这里反向了,记得改三端口微带线的宽

注意,输出端的并联微带线可能有点长,比如分别是7.5mm

那么在输入口,应该也做大一些

可以加两个W为1.62mm的转角,中间再加一个微带线,w也为1.62,因为这种情况对应阻抗为50欧姆,是不会引起反射的

这里可以调节新加的微带线L的长度为8.5mm,保证大一些

类似于这种

再去掉S2p文件,将PA封装干上去即可

最后,将这些去耦滤波电容屏蔽,将1分2那个电阻也屏蔽

用之前的方法导出版图

然后也是新建叠层那一套

如何做板级仿真

去掉MOS管封装,去掉其相应的连接线

在每个对外接线的端口都接上Pin

EM里面单独设置

然后在EM里面,component创建一个EM Model,保存即可

然后切换到有SP2那个文件,因为有封装的是LayOut文件。

切到S2p文件里面仿真

还是点击Library

里面找到我们的Model

直接导入进来

给Sp2文件复制连接代替封装

然后再接电源啊,S参数的Term,再进行S参数仿真

基于晶体管模型的S波段中等功放设计

使用的是电器模型

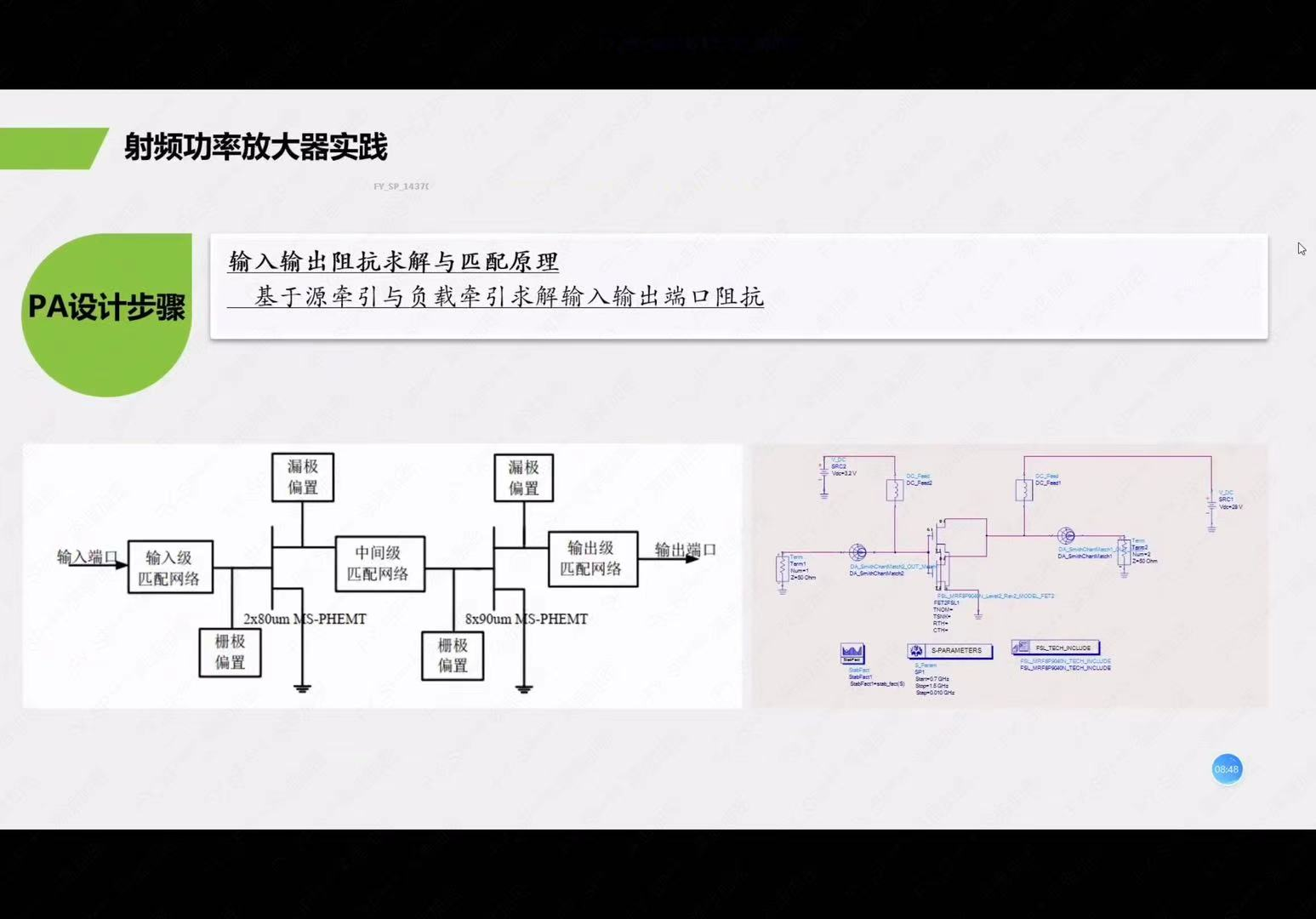

PA的基本设计步骤

1确定设计指标

2晶体管或者场效应管选型

3确定晶体管的静态工作点

4稳定性分析和改善

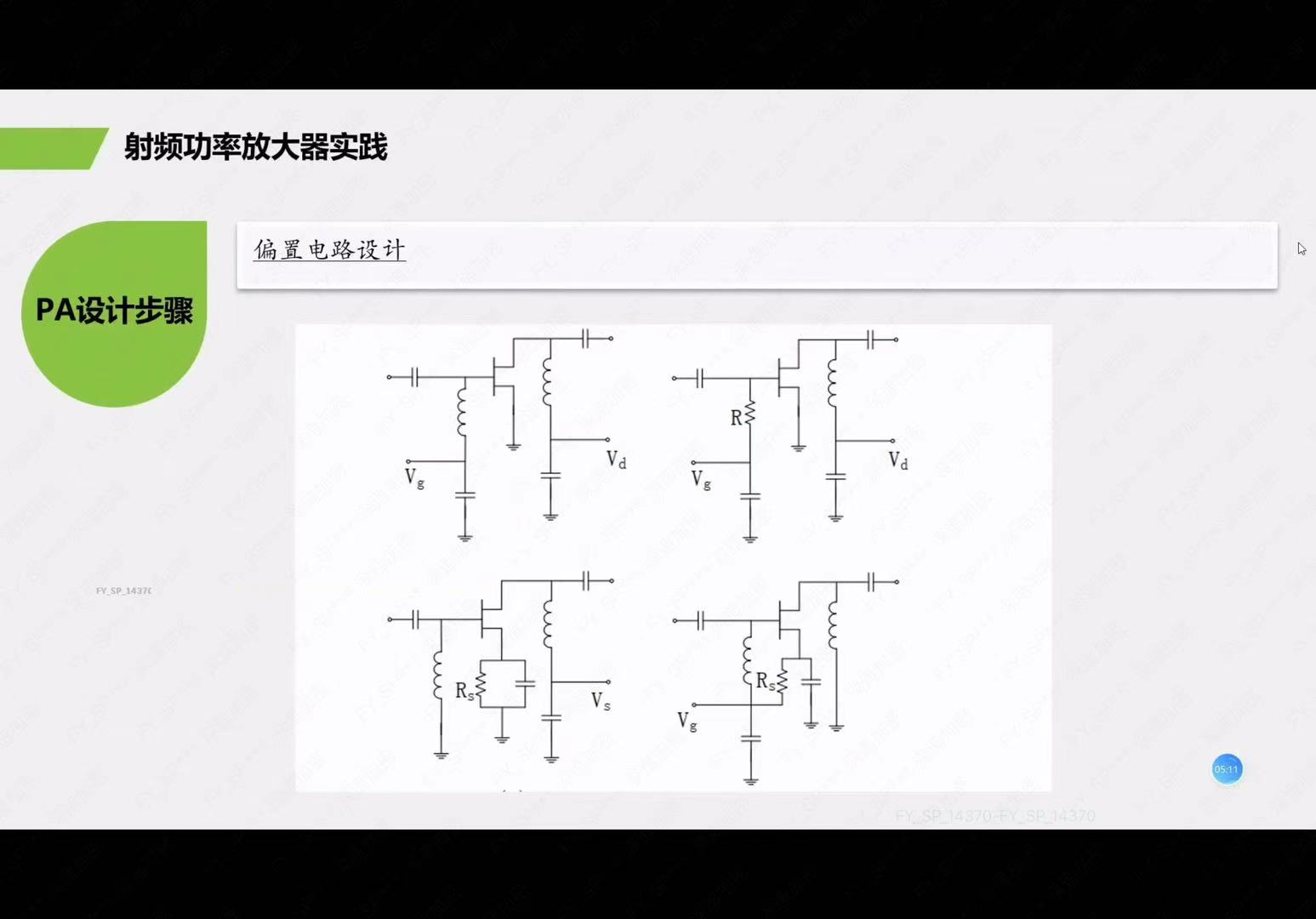

4偏执电路设计

5输入输出阻抗确定和阻抗匹配

6谐波、效率、增益、输出功率分析

7电路仿真和优化

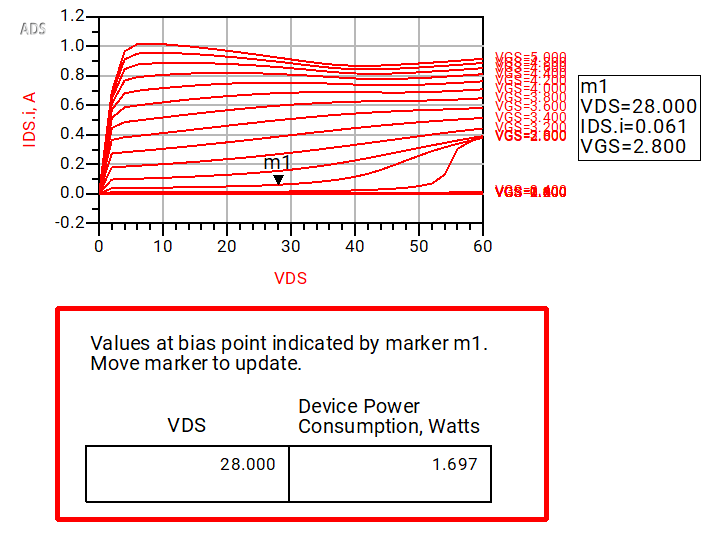

静态工作点确认

对于A类放大器

获得最大的交流信号摆幅,因此将静态工作点尽量放在交流负载线的中点(交流负载线为有交流信号输入时静态工作点Q的运动轨迹)

交流负载线确定:

1是求解交流负载电阻:R’L=RL / / RC

2是过静态工作点Q做一条斜率为 -1/R’L 的直线

偏置电路设计

偏置电路要求输入级要确保管子导通

输出级要确保能提供我们所需要的输出功率

保证交流和直流之间不能相互干扰,加电感隔离交流,加电容隔离直流

稳定性电路设计

降低输入端的功率,通过在输入端串联电阻或者并联RC电路的方法改善,通过电阻消耗或者将部分功率信号引入大地

改善稳定性的同时必定减小PA的效率

要么在输入端引入RC串联电路并联在电源之前

要么直接串联一个电阻

阻抗匹配部分

对于大功率放大器,输入和输出阻抗受实际的输入和输出功率影响,因此,输入和输出的阻抗求解需要考虑实际的功率

输入阻抗匹配原则

基于源牵引技术,求解对应功率下的实际阻抗

输出阻抗匹配原则

由于输出功率较大,晶体管通常工作在极限状态下,因此需要综合考虑晶体管所能承受的最大电压和最大电流

【共轭匹配虽然能满足最大功率输出,但由于晶体管所能承受电流和电压的影响,因此共轭匹配并不能获得理想的输出功率】

输出功率匹配要求:充分利用信号源所能提供的最大功率,优化负载,使到达输出电压和电流的限制条件,也就是负载线匹配。

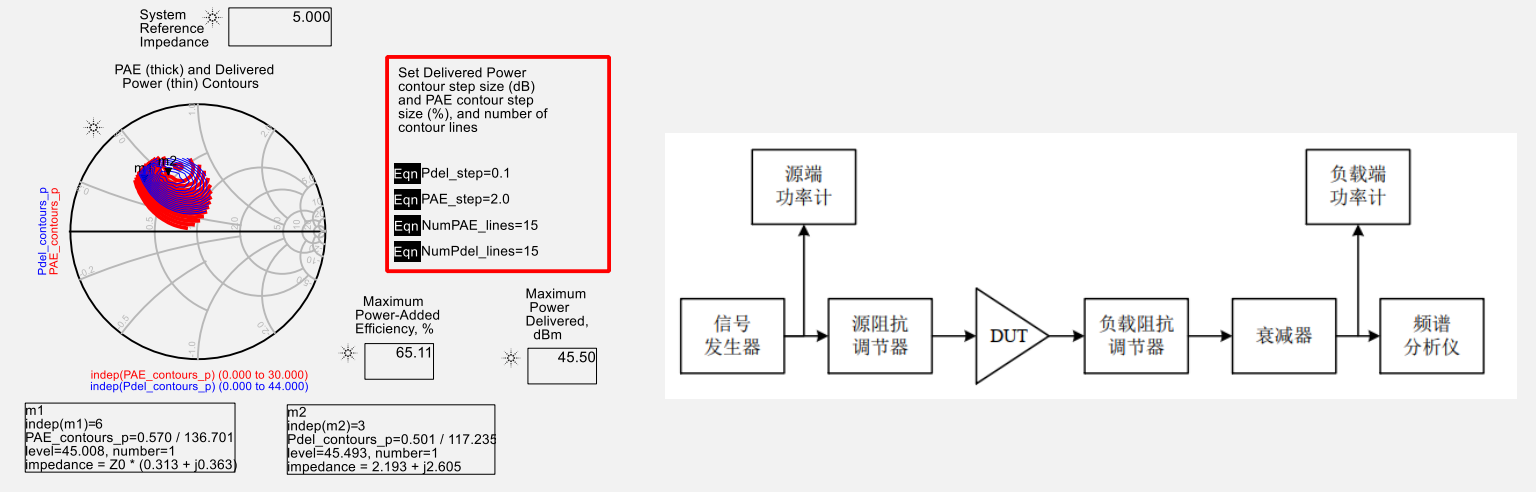

Ropt通过Loadpull曲线获得,即输出功率随负载阻抗的变化曲线

输出输出阻抗求解

1 对于PA,其源端通常采用源牵引

2 负载端采用负载线匹配:通过负载牵引求解输出阻抗,然后进行匹配电路的设计

PA属于大信号放大器,由于晶体管的非线性,随着输入信号功率的增大,晶体管进入饱和状态时,其内部的输出阻抗将会发生变化。因此,在设计功放的输出匹配电路时,往往需要根据设计目标的不同将输出端口阻抗匹配到不同的阻抗点。

负载牵引

进行负载牵引时,通过不断调节源阻抗调节器和负载阻抗调节器,使晶体管连接各种不同的源阻抗和负载阻抗,同时测量出晶体管在连接不同输入输出阻抗时的输出功率,从而得到某偏置条件下晶体管的一系列输出功率圆,最终找出晶体管的输出功率最大时对应的最佳源阻抗和最佳负载阻抗

非线性仿真

非线性指标

[1]效率和输出功率关系;

[2]P1dB压缩点;

[3]三阶交截点;

[4]输出功率和端口阻抗的关系

设计指标

基于MW6S004NT1晶体管设计GPSL1波段功率放大器,要求如下:

[1]输入VSWR<2,输出VSWR<2.5;

[2]增益Gain>16dB;

[3]输出功率Psat>4W,Pin=18dBm;

[4]效率PAE>40%;

[5]输出功率P1dB>35dBm,Pin=18dBm;

[6]三次谐波<-45dBc

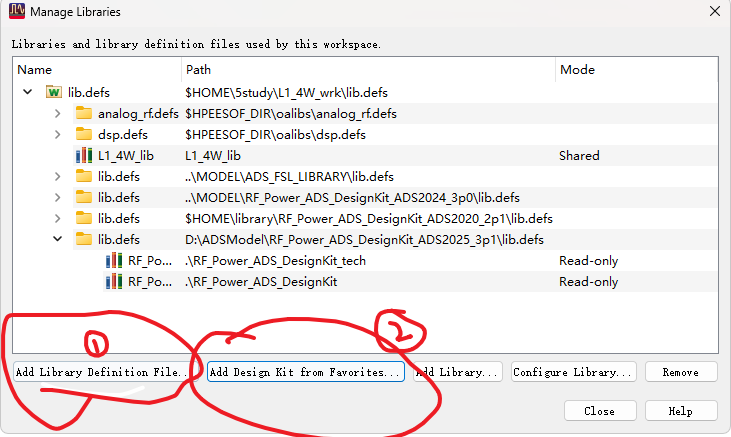

第一步,创建工程且导入ADS库

首先是创建工程,创建的时候打开高级设置,给生成其他文件打开,选择PCB,注意PCB的单位是mm

然后导入库,选择libs文件导入即可

注意ADS使用了NXP的晶体管必须再装一个他的POWER的库

这里如果按照视频教程来安装lib文件还是报错,我们首先应该在设置哪里给他再打勾

第二步,IV仿真

点击insert,点击ads_trmplate:FET_curve_tracer

给FET管子放进去,注意放声明文件

再对照数据手册得知,这是一个增强型的MOS管,这里看到数据手册说栅压最低-0.5v,最高12v,漏压最高68v

所以这边设计栅压Vgs时,初始值给0v,从0扫描到5v,步进设为0.2v

然后Vds这边设计为0v到60v,步进改为2

仿真

参考一下官方给的文档,是最安全的,这里仿真和datasheet不一致,我们以仿真为准

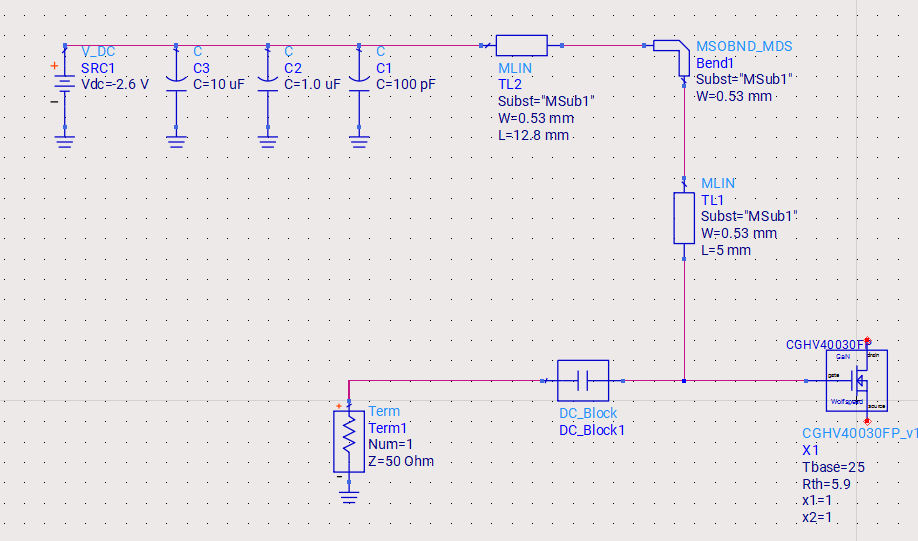

第三步,稳定性分析

新建原理图,选择S参数模型

进去删除S的一个模版,然后插入FETMOS,选择Lumped这里面的,理想隔直电容DC_Block

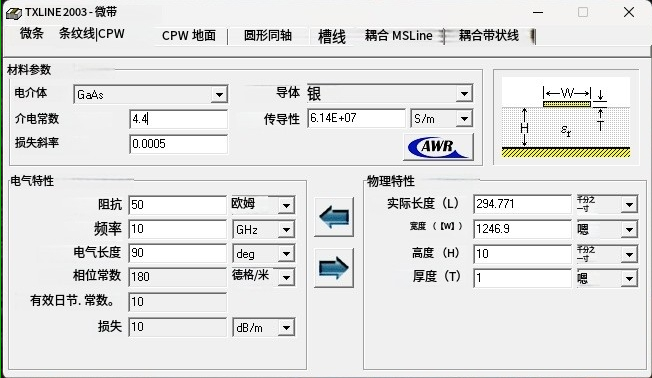

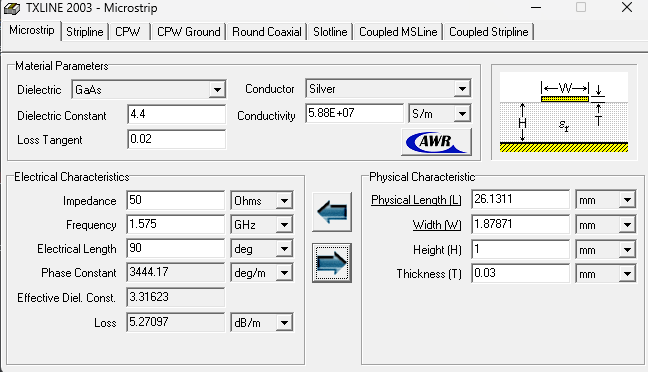

我们直接在这里放置微带线,我们在TXLINE中进行计算

这是TXLINE界面

我们用的是FR4介质基板,所以介电常数是4.4

损耗角正切值是0.02

厚度为1mm,频率是1.575Ghz

点击计算之后得到W和L

找到TLine-microstrip库,先给微带线基板MSUB放下

长度L是26.1,W是1.87

我们先整一个长为15mm的,再整个转角

转角参数:

W (宽度):表示微带线的宽度,当前设置为0.25 mm。这个参数会影响微带线的特性阻抗。

Angle (角度):表示微带线弯曲的角度。这里的设置是45°,意味着微带线弯曲的角度为45度。

M (倍数):倍数是一个缩放因子,用于设计微带线的弯曲部分。当前设置为0.5,表示弯曲部分的长度相对于其他部分的缩放比例。

我们再接一个11.1mm的微带线

再接100pf 1uf 10uf 的电容,漏级电压给28v

S参数改为1到2G,1M的扫频

找到S参数库

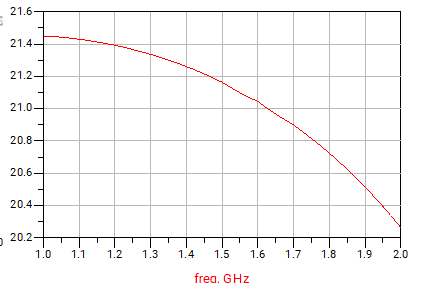

找到最大增益,MAXGain,需要这里符合我们设计要求也就是增益>16dB

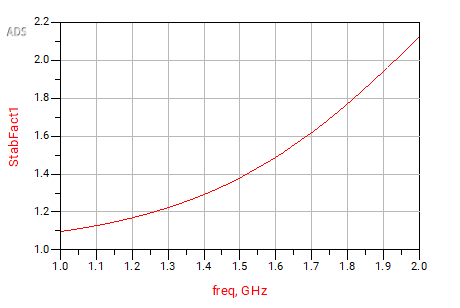

第二个是StabFact,看稳定性的

我们点击仿真,这里先看StabFact,要求是大于1

再看maxGain看是否符合我们要求

保持在20以上,符合我们要求

这里我们实际使用的时候,再加一个小电阻10欧姆即可,在输入并联的微带线部分增加

没问题即可

第四步,阻抗求解

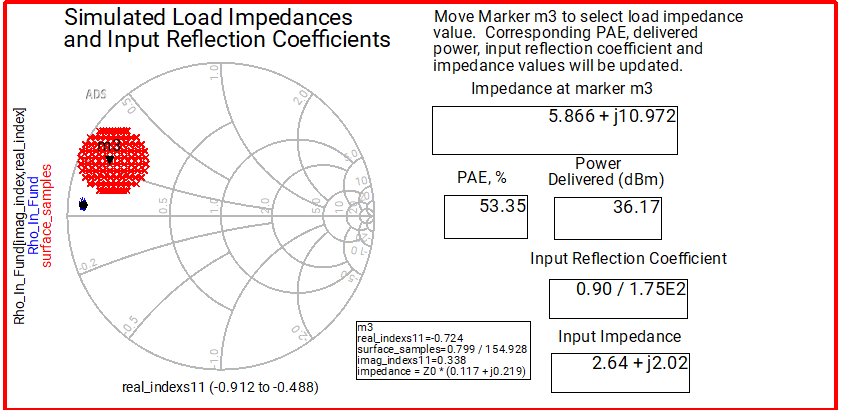

负载阻抗

先对输出阻抗进行负载牵引

点击designguide,点击amplifier,选择Loadpull

将其中不需要的全部删除

将稳定性分析之后的电路,除去TERM和电源以及仿真参数,其他部分主体电路复制进去

之后修改参数

Pavs=18dBm表示我们上面测试能够得到20dBm,这里实际是18dBm左右,参数设置了信号源的平均功率,当前值为 18 dBm,表示信号源的输出功率。

RFfreq就是信号频率

Vhigh和Vlow是漏级和栅极电压

调节到和最大功率和最大效率差不多即可,这边阻抗为5.9+j11

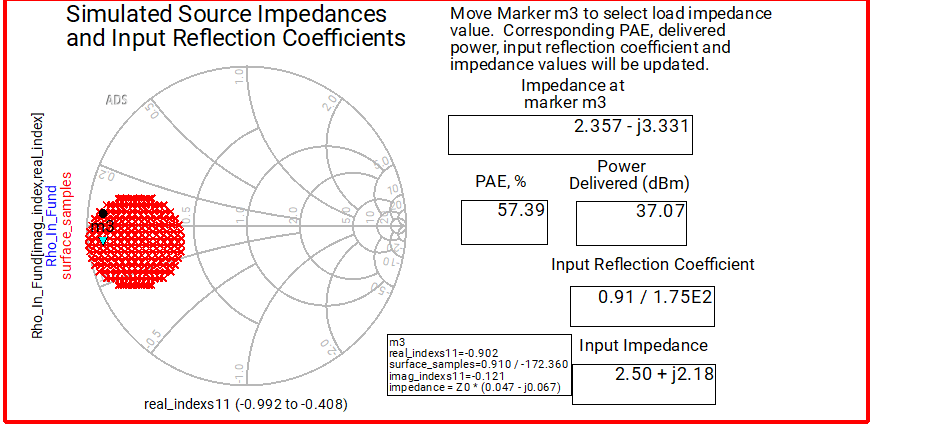

源阻抗

SourcePull

同负载牵引

但是在阻抗部分,需要修改,设置为刚刚Loadpull里面的值,得到2.4-j3.3

第五步,输入输出匹配

新建match文件夹,新建outmatch原理图,导入s参数

OutMatch

这里在调好S参数后,将左边的TERM1的阻值修改为Loadpull的阻抗的共轭值

也就是5.9-j11

再插入Smith圆图

注意这里圆图修改,源端修改的是Zg的值

负载类型改为resistive

最后loadimptype改为输出阻抗

之后就是smith chart匹配

先串一个隔直电容,再串一个微带线,再并一个微带线,再串一个

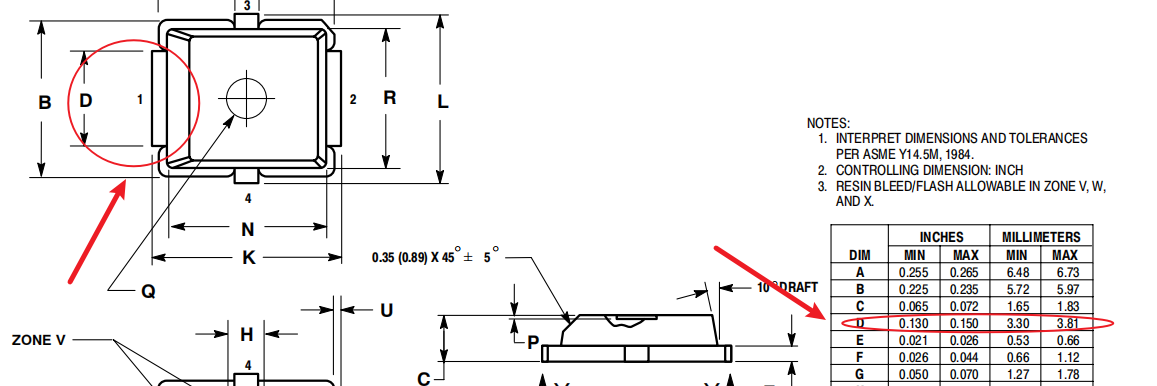

这里就要注意,查看手册看一下MOS管焊盘多大,确定一下最后的微带线宽度

这里D最大是3.8,所以我们最低不能少于3.8mm

这里首先给这个第一级微带线阻抗调小一些,这样他的角度就小一些

前面串联的也可以调小一些

最后一级要设置宽一些,就要给阻抗调更低,这里是18欧姆

然后设置好之后,点击build

然后仿真验证一下

没问题之后,复制MSUB,然后打开实际微带模型库

换成实际微带线库之后,仿真发现没大问题

再进行微带线转换方便我们版图

最后再加入偏置,直接从稳定性哪里给out端复制过去

插入偏置之后,还需要再加一个三端口

Inmatch

和上述方法一致

这里我们给TERM1的阻值为源牵引得到值的共轭

这里在进行匹配的时候,也是电容加微带线

我们设置好之后,再加上我们的偏置

这里注意在分定性分析的时候,我们的输入端是接了一个电阻的,我们在三端口微带线上面加上

保持好一致之后调节参数即可

调节这三个参数即可

这里我们前面的工作做完了

第六步,整合

先看S11、S22、S21

我们回到稳定性电路这里,除了仿真参数那两个,其他的全部复制

新建原理图PA_Layout

给输入输出的也接上去,全部粘贴在这里

点击仿真之后还要做微调

先调输入再调输出,因为管子有反向隔离效果,改输入会影响输出,改输出不会影响输入

这里使用仿真按钮右边那个,可以一起调

打开之后选中器件,然后微调,给步进改为0.5,整好之后记得点更新到原理图,然后点关闭

两边都调好了之后,查看驻波比

看驻波比

搜索VSWR,看S11和S22的驻波比,上面我们设计指标中有要求

VSWR_S11 < 2

VSWR_S22 < 2.5

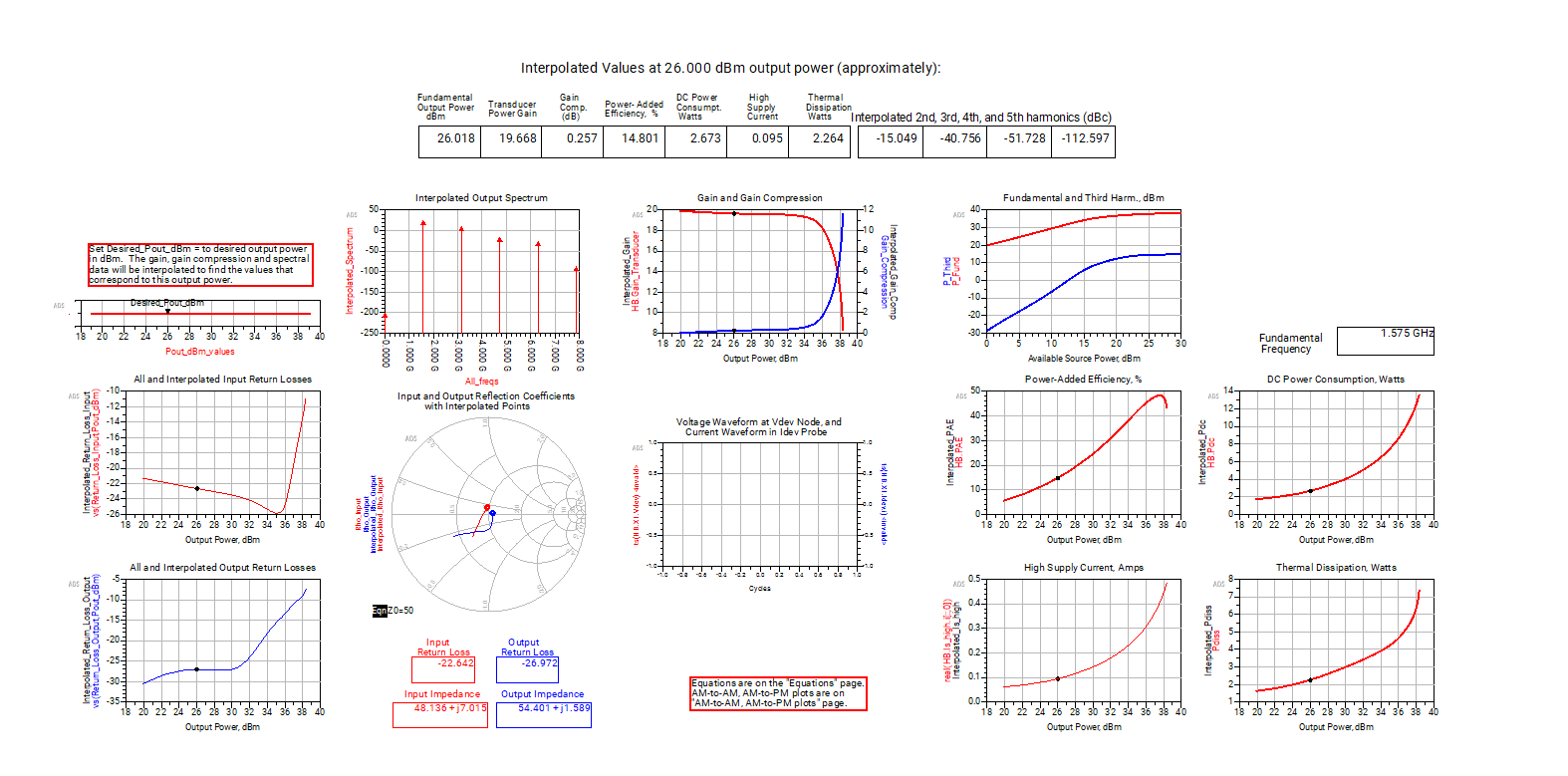

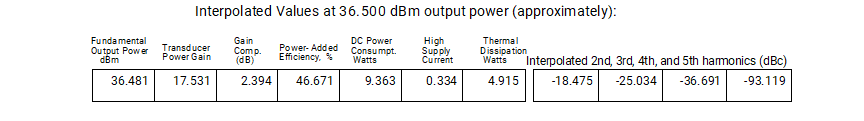

第七步,非线性仿真

仿真操作

在design guide里面选择单音测试,选第四个Gain,Harmonic,Distortion vs Power (w/PAE)

将原始部分去除,用我们刚设计好的

手册给的最大输出4W,所以给扫描的最大值改为30(两个都改)

这里显示为仿真结果

左边第一个是输出功率,改为36dbm大概就是4w,

效率

看表格第四个

输入为4w,效率是46%

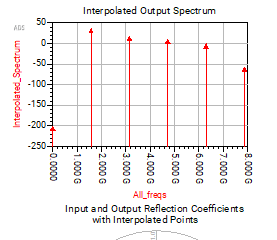

谐波

第二个是频谱图,展示的是谐波

这里打点可以看到,谐波抑制比是18dBC

1dB压缩点

点击右下角x-dB Gain Compression

第八步,做版图

和之前一样,先不学了

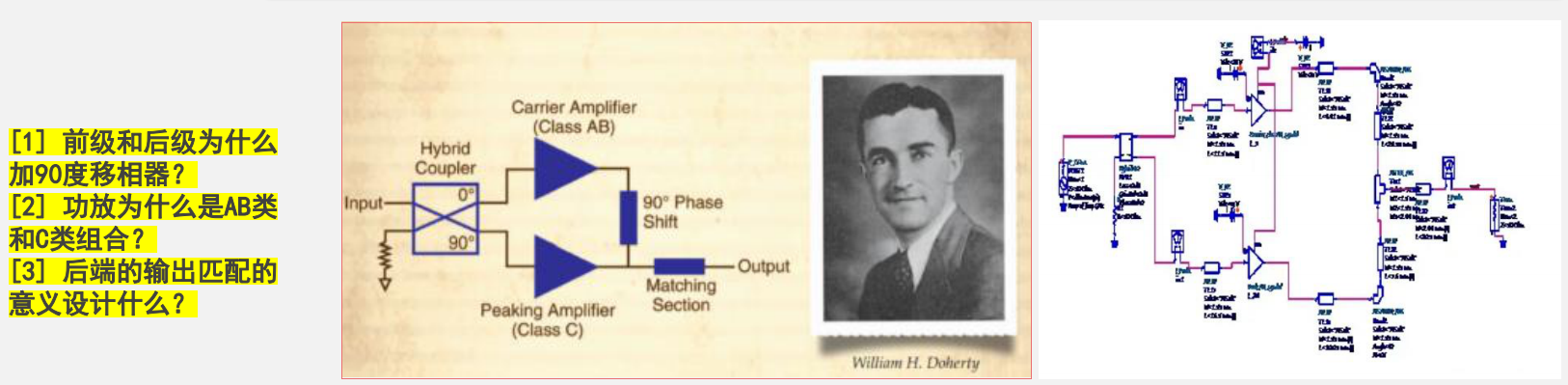

Doherty理论

介绍与优缺点

Doherty是通过结合两个两个不同功率级别的放大器,一个主放大器和一个辅助放大器,来提高效率。通过这种合作的方式,Doherty放大器在维持较高的功率效率的同时,还能保持较低的失真水平。

优势:实现较高的效率水平,技术没有包络跟踪复杂。

缺点:

很难在很宽的带宽上保持分路器的相移,因此其不能用于宽带多用于窄带

成本高于单极放大器,设计不易进行,很难获得最佳性能

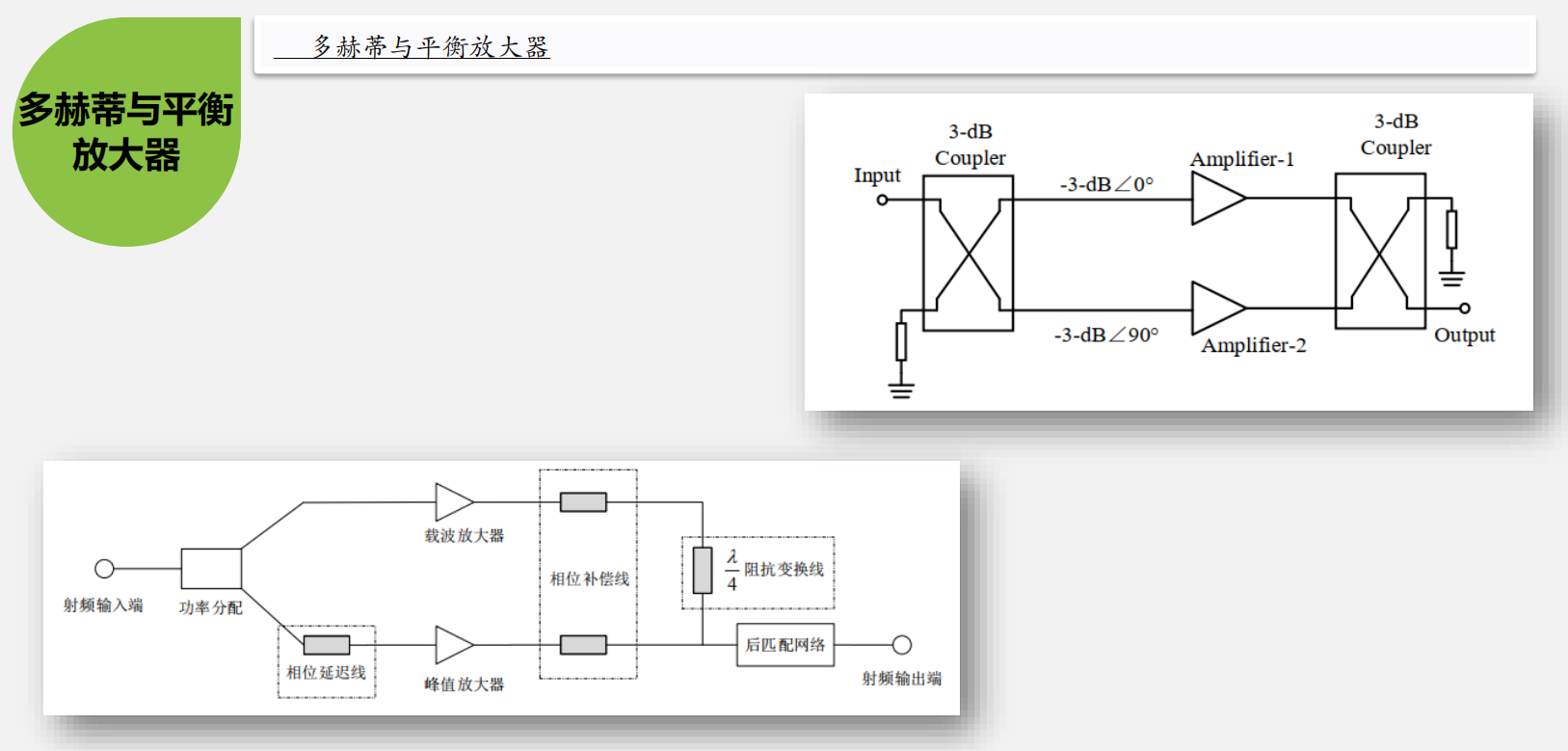

和平衡放大器的区别

平衡放大器

平衡放大器通常由两个相同的功率放大器单元(通常是A类、AB类或B类)和两个90度混合耦合器(Quadrature Couplers,或称作Hybrid Couplers)组成。

架构:

- 输入端: 一个90度混合耦合器将输入信号分成两路,这两路信号相位差90度(例如,一路0度,一路90度)。

- 放大器单元: 这两路信号分别馈入两个独立的、特性相近的功率放大器单元(PA1和PA2)。

- 输出端: PA1和PA2的输出信号再通过另一个90度混合耦合器进行合成。

工作原理:

- 信号分裂与合成: 90度混合耦合器是关键。在输入端,它将信号分为两路,例如一路到PA1(直通端口,0度),一路到PA2(耦合端口,-90度或+90度)。在输出端,耦合器再次合成这两路信号。

- 阻抗匹配与反射抑制: 如果两个PA单元的输入/输出阻抗匹配良好,耦合器能将反射信号(来自PA输入端或输出端的不匹配)导向其隔离端口,而不是返回到源或输出负载,从而改善VSWR。

- 偶次谐波抑制: 由于信号在两个PA之间是90度相位差,当它们在输出端合成时,偶次谐波(如二次谐波)会因相位抵消而被抑制,从而提高线性度。

- 鲁棒性: 如果其中一个PA单元失效,另一个PA仍然可以继续工作,尽管输出功率会降低。

优点:

- 优异的输入/输出VSWR: 反射功率被隔离。

- 良好的线性度: 偶次谐波抑制,尤其是在B类/AB类PA中。

- 模块化和可扩展性: 易于并联更多的PA单元。

- 一定的容错能力: 一个PA失效不影响另一个。

缺点:

- 需要两个独立的PA单元: 增加了成本和复杂性。

- 需要两个高性能的90度混合耦合器: 它们会引入损耗,降低整体效率。

- 效率提升不明显: 主要侧重于线性度和VSWR,而不是效率。

Doherty

Doherty放大器是一种基于负载调制(Load Modulation)原理的效率增强型PA架构,旨在提高功率回退时的效率。它通常由一个主放大器 (Main Amplifier) 和一个辅助放大器 (Auxiliary/Peak Amplifier) 组成。

架构:

- 输入端: 一个功分器(通常是0度功分器,如Wilkinson功分器或简单的分压器)将输入信号分成两路。

- 主放大器 (Main PA): 通常偏置在AB类或B类,处理低功率到中等功率范围。

- 辅助放大器 (Auxiliary PA): 通常偏置在C类或深度AB类,在低功率时不工作,只在达到一定功率阈值后才导通并贡献功率。

- 相移网络 (Phase Shift Network): 在主PA或辅助PA的输入端或输出端,会有一个相移网络,确保在峰值功率时,两个PA的输出信号能够同相合成。通常是一个90度的相移器。

- 组合器 (Combiner): 一个特殊的阻抗变换网络(通常是四分之一波长传输线)用于合成两个PA的输出,并实现负载调制。

工作原理:

- 低功率阶段: 只有主放大器工作。辅助放大器处于截止状态(或接近截止)。此时主放大器在相对较低的输出功率下以高效率工作(例如,接近饱和点)。

- 中高功率阶段(拐点以上): 随着输入功率的增加,当主放大器接近其饱和点时,辅助放大器开始导通。

- 负载调制: 辅助放大器导通后,其输出信号通过组合器网络(通常是四分之一波长线)反射回主放大器,有效地改变了主放大器的输出阻抗。这使得主放大器在输出功率继续增加时,能够维持其负载在最佳效率点(例如,接近高阻抗状态),从而避免过早饱和并保持高效率。

- 峰值功率阶段: 两个放大器都全功率工作,并将功率合成到负载。此时,辅助放大器也以高效率工作。

优点:

- 显著提高回退功率时的效率: 这是Doherty的核心优势,尤其适用于蜂窝基站等需要高线性度且具有高峰均比(PAPR)的复杂调制信号的应用。

- 节省能源和降低散热需求。

缺点:

- 设计复杂: 需要精确的偏置点控制、相移网络和负载调制网络。

- 带宽有限: 负载调制网络(尤其涉及四分之一波长线)通常是窄带的。

- 线性度挑战: 两个不同偏置的放大器在功率切换点(”knee” point)处容易产生非线性失真,需要更复杂的预失真 (DPD) 技术来校正。

- 对器件匹配要求高: 两个PA单元的特性和相移的精确控制对性能至关重要。

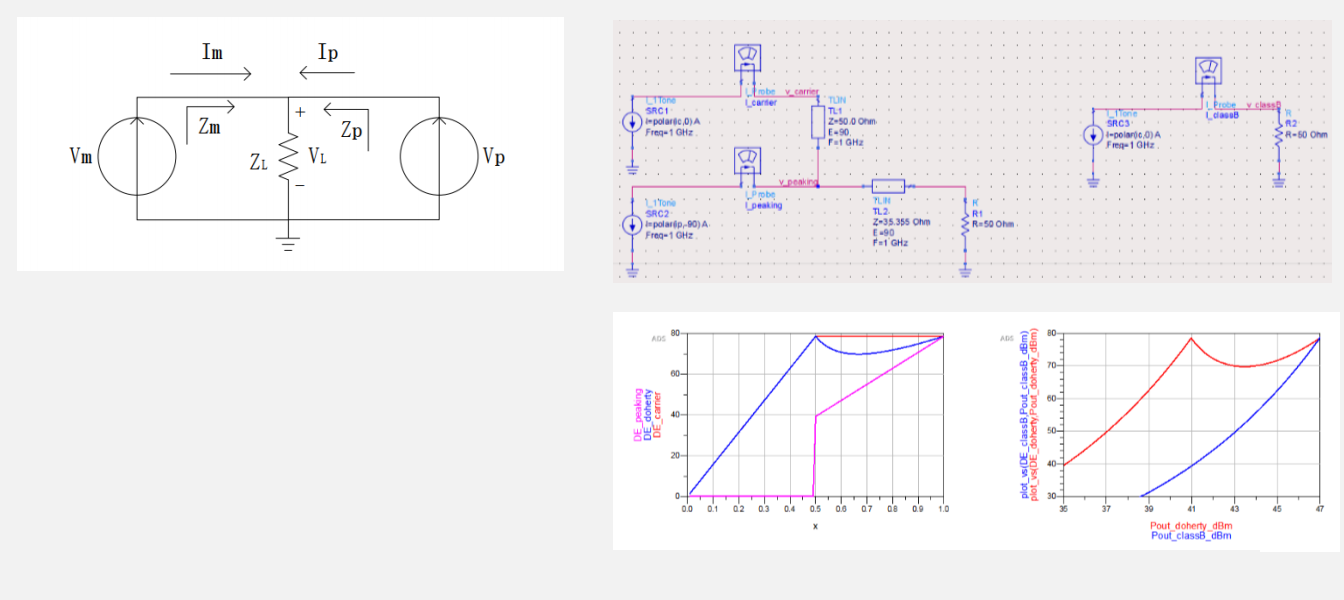

负载调制原理

负载牵引

Vm和Vp是两个电流源

假设Vp断开,这里VL=RIm,Zm=(Im R )/Im

Vp不为0,此时VL=R*(Im+Ip)

Zm=VL/Im=R(Im+Ip)/ Im

这里我们就会发现,对于Vm的输出阻抗而言,是受到Vp的影响的,所以当Vp越大,其输出阻抗越大

随着Ip的的增加,Vm的视在阻抗跟着增大;由电流源Ip对电流源m的阻抗调制的方式就是负载牵引。

负载调制

在射频功率放大器中,负载调制是指在输出功率变化时,动态地改变放大器管芯(例如:晶体管)所“看到”的输出负载阻抗。

为什么需要这样做?

- 最佳工作点: 任何功率放大器晶体管都有一个“最佳负载阻抗”,在该阻抗下,它能以最高效率输出最大功率。这个点通常被称为“饱和点”或“压缩点”。

- 效率下降: 当放大器输出功率低于最大饱和功率时(即处于功率回退状态),如果其负载阻抗保持不变,那么它的效率会急剧下降(线性的)。这是因为在回退功率下,晶体管并非全饱和导通,其电压和电流波形并非理想的矩形波或半正弦波,导致大部分能量以热量的形式耗散在晶体管内部。

- 目标: 负载调制的目标是,在放大器输出功率下降时,动态地调整其输出负载阻抗,使得晶体管在回退功率下也能工作在接近其最佳效率的负载阻抗,从而维持较高的效率。

负载调制的基本原理

核心思想是,通过某种机制(通常是另一个放大器或一个开关),在主放大器输出端的负载网络中引入一个额外的、可变的反射。

工作流程(以Doherty放大器为例):

- 低功率区:

- 只有主放大器工作。

- 辅助放大器处于截止状态(或深度截止)。

- 此时,辅助放大器看出去的阻抗非常高(接近开路)。

- 负载调制网络(通常包含一个四分之一波长传输线)会将这个高阻抗变换成一个非常低的阻抗(接近短路),并反射回主放大器的输出。

- 因此,主放大器在低功率时看到的负载阻抗被“拉低”到一个较低的、能使其在该功率下高效工作的点(例如,接近50欧姆系统阻抗)。

- 中高功率区(拐点):

- 随着输入功率的增加,主放大器开始进入饱和区。

- 此时,辅助放大器开始导通,并向负载贡献功率。

- 辅助放大器的导通状态和输出阻抗开始发生变化。

- 负载调制网络会将辅助放大器的可变阻抗,以一种非线性的方式,反射回主放大器的输出。

- 主放大器因此看到的负载阻抗会逐渐“抬升”到一个较高的阻抗值。

- 这种阻抗抬升使得主放大器在超过其“最佳效率饱和点”后,依然能保持高效率,因为它的有效负载阻抗被动态调整了。

- 峰值功率区:

- 主放大器和辅助放大器都工作在饱和状态,共同向负载提供最大功率。

- 此时,两个放大器都工作在它们各自的最佳效率负载点。

实现负载调制最常用的技术是利用四分之一波长传输线

四分之一波长传输线的阻抗变换特性: 一个特性阻抗为

在Doherty中的应用:

- 假设系统负载为

(通常是50欧姆)。 - 在主放大器的输出端和最终负载之间,通常会放置一个四分之一波长传输线(或者更复杂的网络)。

- 辅助放大器的输出通过一个支路连接到这个传输线的中点或通过另一个四分之一波长线。

例如:当辅助放大器关断时,它看出去是高阻抗(

)。如果通过一个四分之一波长线变换,这个高阻抗会变成低阻抗,并“拉低”主放大器的负载。当辅助放大器导通并向负载提供功率时,它会呈现一个变化的阻抗,通过四分之一波长线的特性,这又会反过来调制主放大器的有效负载。 - 假设系统负载为

Doherty原理

看完前面的也就懂了原理

Doherty是一种效率增强技术,通过主动负载牵引来调制晶体管阻抗

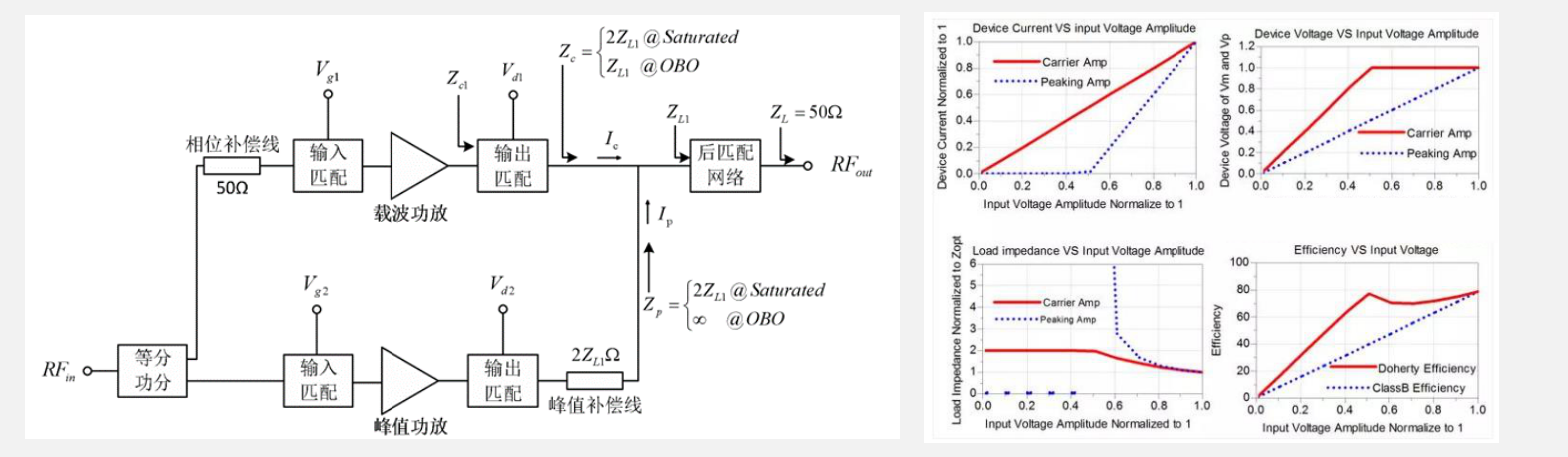

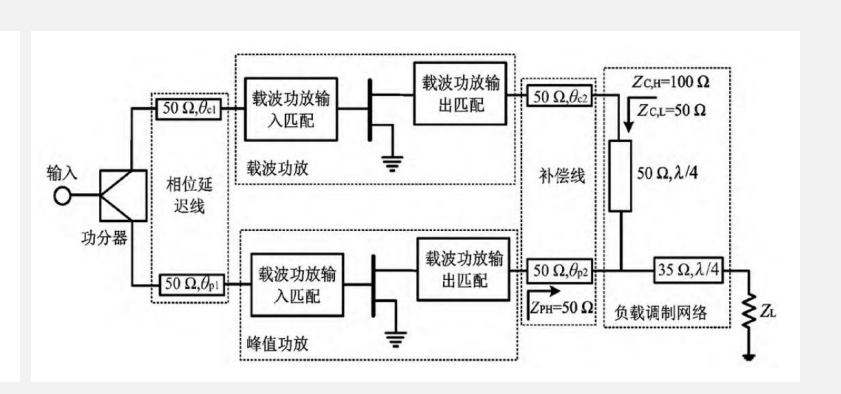

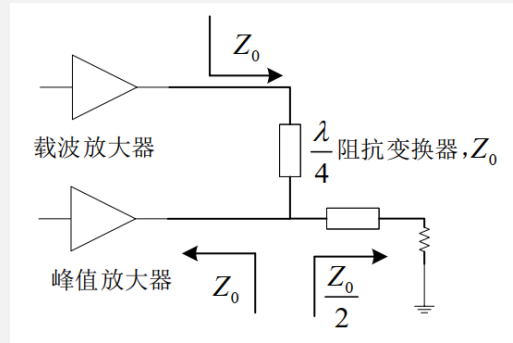

Doherty架构

两路功放偏置的工作状态不同,主功放偏置在 AB 类,辅助功放偏置在C类。当对称 Doherty 两路输入相同功率时,两管不同的工作状态使得辅助功放管的输出电流小于主功放管的电流,从而辅助功放管的输出功率小于主功放管。

Doherty放大器工作原理

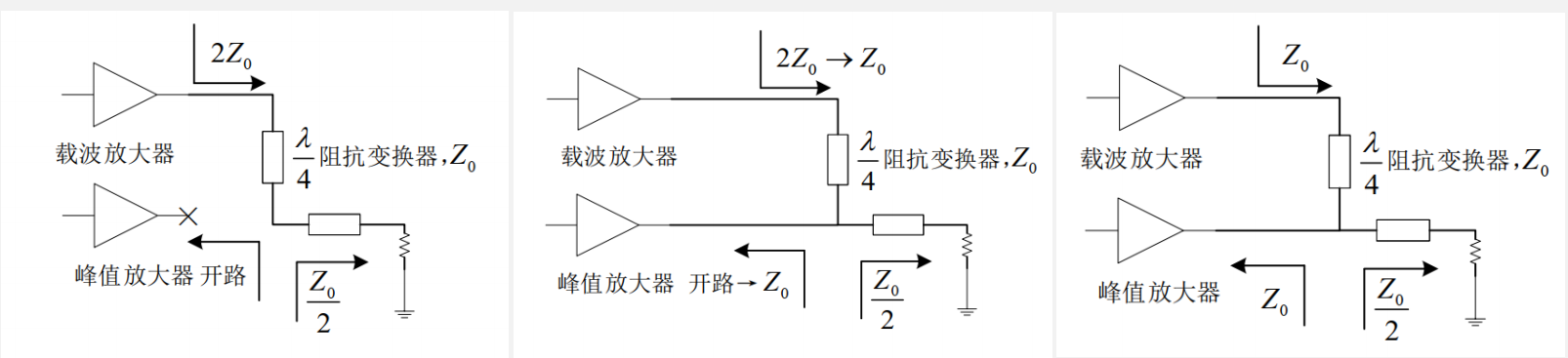

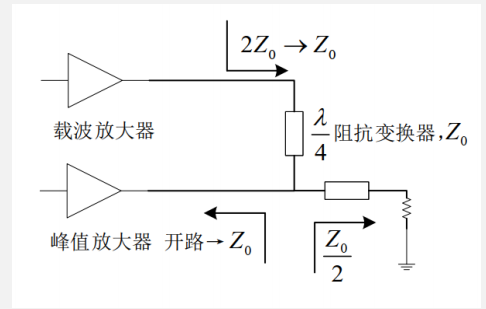

[1]小功率输入状态(依赖于0.25波长匹配线强制匹配,提高载波放大器输出阻抗值)

[2]中功率输入状态(依赖于主功放输出电流的有源负载调制,提高载波放大器输出阻抗)

[3]大功率输入状态(依赖于放大器本身的效率,载波功放进入饱和区,C类功放正常工作)

小功率

峰值放大器(C类)(也就是我们所说的辅助放大器)此时断开,为开路。此时载波放大器(AB类)输出电流为

负载阻抗为50Q,后匹配的0.25波长匹配线为35欧姆,50欧姆通过35欧姆匹配线到25欧姆,25欧姆通过50欧姆0.25波长匹配线得到100欧姆,100欧姆即为AB类功放的视在阻抗(输出阻抗)

因此视在功率$ P= {I_1}²m=2 I²*Z_0 $,相对传统放大器,视在功率增加1倍,因此输出效率提高。

中功率

中功率下,载波放大器输出功率变大,效率提高;峰值放大器逐渐开启,输出电流,因为C类放大器本身的效率较高,因此重点分析载波放大器的输出阻抗;

载波放大器的输出阻抗受峰值放大器的输出电流牵引,输出阻抗变大,视在功率提前进入饱和,此时载波放大器获得最大输出效率。

大功率

载波放大器和峰值放大器都处于饱和输出状态,此时放大器本身到达了最大效率,两个放大器自身的输出阻抗均为50欧姆,和后端完全匹配。

总结:小功率靠匹配,中功率靠调制,大功率靠自己

设计思路方案

峰值放大器输入端的0.25波长的传输线为载波放大器输出0.25个波长匹配线的相位补偿段:保证两路功放在功率合路端的相位是一致的。

输入端分路方案:

[1]威尔金森功分器+0.25波长传输线(确保两个分支的隔离度>25dB);

[2]采用3dB桥式耦合器方案,耦合端输出相位滞后于直通端90度,此时不需要单独添加0.25波长的相位补

偿线。

所以,AB类之后接的四分之一波长微带线是做匹配用的,最前面的四分之一波长微带线做相位补偿用的

Doherty设计

AB类

DC部分

首先还是和之前一样的步骤,先进行DC仿真,得到静态工作点

然后进行稳定性分析

稳定性分析都是用的微带线进行处理

计算得到长度12.8mm,宽度是0.53mm

还是先并微带线,转角,串微带线,加3个电容,加电源

注:

这里我们加DC_BLOCK的目的是,隔直电容隔绝直流信号进入射频源。

加四分之一波长微带线(也就是所说的三个微带线)的目的,是防止射频源进入直流Vdc里面。

之后稳定性测试,查看MaxGain和Stab的值

Loadpull和SourcePull

这里其实可以不用将微带线带入来跑,也可以直接带管子即可,就是后续要调,这里用这种方法

这里loadpull的PAvs这里是输入功率,我们小信号增益大概是20dB,大信号是少6个dB,所以是14dB左右。我们设置输入为30dBM

大概输出为44dBM

之后就是对其仿真即可

输出阻抗loadpull得到6.7+j*5.0,sourcepull的到结果是1.2-j9.8

match

和之前一样先进行输出阻抗match

将端口2向端口1进行匹配,这里端口1设置为loadpull的共轭阻抗,6.7-j*5

再总结一下匹配时候微带线的问题

首要要求就是你的管子焊盘宽度要小于微带线宽度

所以要求我们微带线要宽,那么影响微带线宽窄的因素是什么呢?

是电阻值,电阻越大,微带线越窄;电阻越小,微带线越宽。

同时我们有串联微带线和并联微带线

由于串联微带线需要承载电流,而并联微带线不太承载电流

所以串联微带线要宽,并联微带线可以不用做的太宽

simth圆图的问题

当我们在匹配时,他这个有bug,会自动共轭

所以我们应该看一下点在哪里

如果是左上角表示虚部是正的

在左下角说明虚部是负的

他会自动给你共轭上去

也就是说,如果你loadpull出来虚部是正的,那么你匹配的时候term设置为共轭的负的,但是你在做smith tool匹配时,图上显示是正的,这种情况是正确的

同理可得虚部是负数的情况

c类

C类也就是在AB类基础上继续降低栅压,这样就是C类

这里我们栅压调整为-3.8v

发现和-5v效果一样的,我们在-5v下面跑这个仿真,在loadpull下发现有70%的效率,这时就处于c类

有的时候真觉得没意思,b玩意卡学历,学也用不上

整合

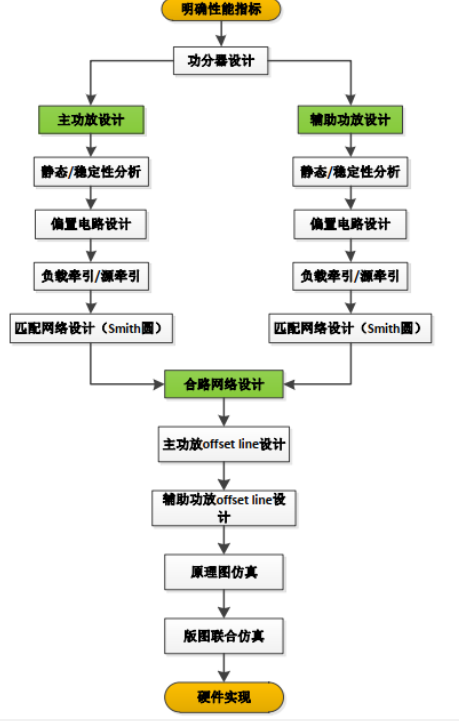

这是整体设计流程

设计C类的时候,只需要改AB类的偏置即可

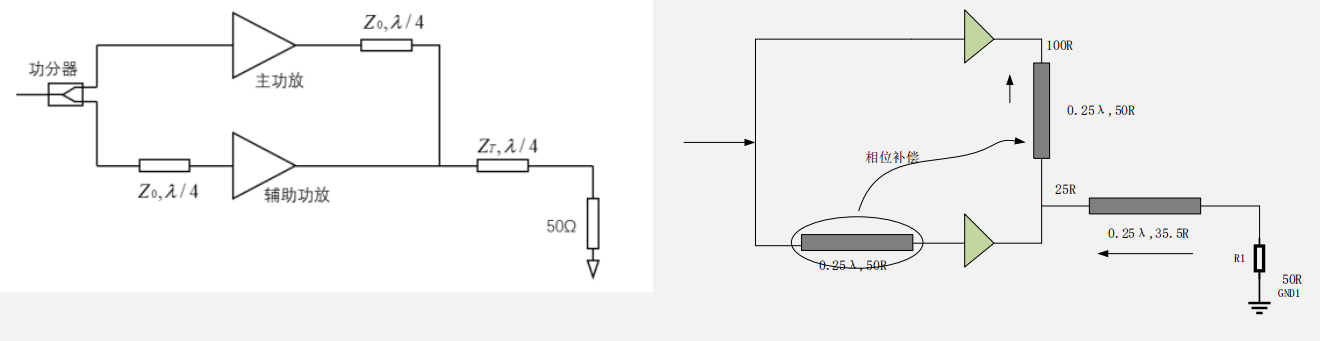

3dB耦合器(电桥)

在Doherty中,3dB90°定向耦合器又被称之为3dB电桥

这是一个非常关键的无源器件,它的作用不仅仅是分配功率,更重要的是提供精确的相位关系。

核心功能

理想的3dB90°定向耦合器有4个端口定义为:

- 输入端口 (Port 1, Input) 信号从此处输入。

- 直通端口 (Port 2, Through) 大部分信号从此输出,相对于输入信号有 -90° 的相移。

- 耦合端口 (Port 3, Coupled) 另一部分信号从此输出,功率与Port 2相等,但相对于Port 2有 -90° 的相移(即相对于输入有 -180° 相移)。

- 隔离端口 (Port 4, Isolated) 在理想情况下,没有功率从此端口输出。

它的两个核心功能是:

- 功率分配:将输入功率平均分配给两个输出端口(直通端口和耦合端口)。

- 相位控制:在两个输出端口之间产生90°的固定相位差。

Term1是输入端口,Term2时直通端口,Term3是耦合端口,Term4是隔离端口

计算方法

最常用的形式是分支线耦合器。其结构由两条平行的主传输线通过两条λ/4长的分支线连接而成,形成一个闭合环路。

- 所有线段的长度(L)在中心频率(f₀) 下均为 四分之一波长(λ/4)。

- 分支线(垂直)的特性阻抗记为 Z_b。

- 主线(水平)的特性阻抗记为 Z_a。

传输线计算:阻抗值的推导

电桥能正常工作(功率均分、端口匹配、高隔离度)的关键在于正确选择 Z_a 和 Z_b 的值。

推导目标:找到 Z_a 和 Z_b 的值,使得:

- 输入端口(Port 1)匹配(无反射)。

- 隔离端口(Port 4)无输出。

- 输入功率在Port 2和Port 3上平均分配。

计算过程后续补,微波工程没学看不懂计算方法

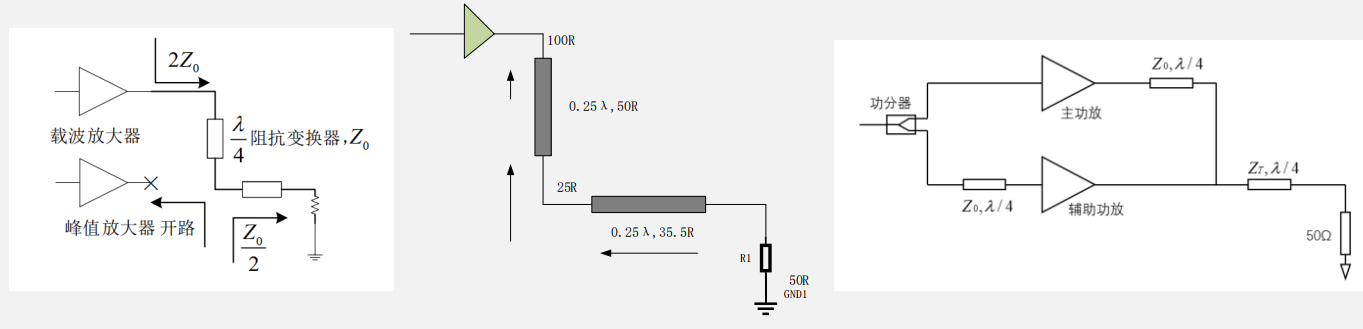

3dB电桥部分竖着放的部分是垂直臂,是50欧姆。横着放的是水平臂,是35.5欧姆。计算方法是50欧姆除以根号2等于35.5。都是四分之一波长

剩下四个都是常规转接线。

新建一个文件夹Doherty,添加子文件夹NET,新建cell,couple_3dB(耦合器),选择S参数模版

在设计好后进行仿真验证,先看回波损耗S11,S22,S33

再看插入损耗S12和S13

再看S12和S13的相位,看一下是不是90°

再设计后级匹配

在两级输出之间先加入四分之一波长微带线,方便连接加一个三端口微带线,两者并联相当于50欧姆并联50欧姆,得到的结果就是25欧姆。

再匹配到负载就是需要再接入一个四分之一波长35.5欧姆的一个微带线,这时候就匹配到了50欧姆

最后在加一个50欧姆过渡线即可

这时整体就组合在了一起,查看S22和S11和S33,看S22是不是完全匹配,S11和S33会相互有干扰

将端口3屏蔽(辅助放大器),端口1改为100欧姆,查看S11和S22是不是完全匹配。

整合

在此基础上,将所有的东西全部都整合

电桥部分的隔离端口(Term4)改为50欧姆电阻接地即可,形成一个吸收效应。

再进行仿真验证即可

输入由Term1进入电桥,直走就是0°,下面就是-90°的移向。

总结

设计主要模块是主功放和副功放,再就是前级电桥和后级匹配

宽带功放设计

宽带放大器架构

分布式放大器

原理是行波传输式的放大器

各晶体管栅极与漏极都连接在对应的传输线上,其中栅极传输线的特性阻抗为 Z0g 和长度为lg ,漏极传输线的特性阻抗为 Z0d 和长度为ld 上。这种架构背后的关键思想是级联多个晶体管以增加增益,同时它们的寄生电容吸收到传输线中,以实现宽的带宽。

由于晶体管受到增益-带宽积恒定定律的影响,带宽和增益不可兼得,所以分布式放大器的设计哲学是革命性的:既然寄生电容无法消除,那就不要把它们看成孤立的、有害的元件,而是把它们作为传输线的一部分“吸收”进去,让它们成为构建一个新型人工传输线的有益元件。

通过级联多个晶体管提高增益,顺便将晶体管的寄生电容融入到传输线结构中,从而获得远比单个晶体管高的截止频率。

分布式放大器由两条平行的传输线构成:

- 栅极人工传输线(Gate Line):由一系列电感(或高阻抗微带线)段

Lg和晶体管的栅极电容 Cgs 组成。 - 漏极人工传输线(Drain Line):由一系列电感(或高阻抗微带线)段

Ld和晶体管的漏极电容 Cds 组成。

- 栅极线的工作原理

- 输入信号从栅极线的左端(输入端)注入。

- 信号沿着这条线以行波的形式向右传播。

- 每经过一个节点(一个晶体管栅极),一部分信号被电容Cgs分流,但大部分信号继续向前传播,并在每一个节点上激励对应的晶体管。

- 由于传输线的特性,只要信号频率低于该人工传输线的截止频率,信号就不会被强烈反射,从而实现了宽带宽的输入匹配。

- 漏极线的工作原理

- 每个被栅极信号激励的晶体管都会产生一个放大后的电流,并注入到漏极线的相应节点。

- 这些电流信号在漏极线上向左右两个方向传播。

- 向左传播的信号:最终会被漏极线终端的匹配负载(通常是50Ω)吸收并消耗掉。这是不需要的能量。

- 向右传播的信号:所有晶体管产生的、向右传播的信号波在输出端(漏极线右端)同相叠加。

关键点在于信号的相干叠加

也就是说为了使所有晶体管贡献的信号在输出端完美叠加,必须保证信号波在栅极线上的传播速度与产生的放大波在漏极线上的传播速度相等。即

- 栅极线特性阻抗

Z0g = sqrt(Lg / Cg),其中Cg主要是Cgs - 漏极线特性阻抗

Z0d = sqrt(Ld / Cd),其中Cd主要是Cds - 相速度

Vp = 1 / sqrt(L * C)通过精心设计Lg,Ld的值,使得1 / sqrt(Lg * Cgs) = 1 / sqrt(Ld * Cds),即可实现相速匹配。