基于 GaAs 工艺高效率功率放大器研究与设计

常用指标

1dB压缩和三阶交调

- P1dB(输出 1dB 压缩点功率)

当放大器的增益因非线性效应下降 1dB 时,对应的输出功率值。此时输出功率比理想线性增益下的值低 1dB,是衡量放大器线性工作范围的重要指标。 - Pin_max(输入 1dB 压缩点功率)

就是此时的输入功率 - Gain(放大器的线性增益)

放大器在未压缩(线性工作区)时的增益,单位为 dB。例如,若输入功率为 0dBm,增益为 20dB,则理想输出功率为 20dBm。 - -1dB(增益压缩修正项)

因放大器非线性导致的增益下降 1dB 的补偿项。它反映了实际输出功率比线性输出减少 1dB。

三阶交调量与基波信号的差值

输出功率

峰值转为有效值计算

效率,相邻频道泄漏比

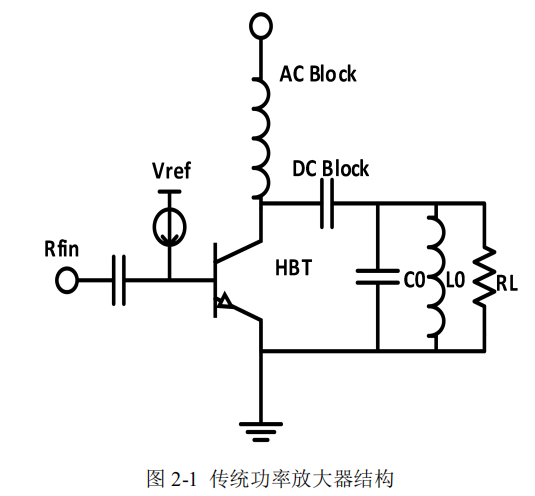

传统功率放大器

谐振电路的作用:

在谐振频率下电阻电容的相互作用会抵消,最大化信号传输。可以使电路对特定频率的信号具有选择性,允许信号的放大或滤波。例如,射频功率放大器需要对输入的射频信号进行放大,谐振电路可以确保仅在特定的工作频率范围内有效地放大信号。

当电路处于谐振状态时,它的阻抗通常是最小的(对于串联谐振电路)或最大的(对于并联谐振电路)。通过谐振,能够有效地将信号源与负载之间的阻抗匹配,从而减少信号的反射和损失,提高功率传输效率。

在谐振频率附近,电路对输入信号的响应会显著增强,这意味着信号的幅度会被有效放大。例如,在一个射频功率放大器中,通过调整电感和电容的值,使其工作在某个特定频率下,信号的放大效果会最为明显,从而提高输出功率。

可以滤波

电路稳定性

通过计算S参数来判断系统稳定性。

其中,

当 k>1 且Δ<1 时,电路绝对稳定

在信号输入端加入一定数值的阻抗可以有效地防止晶体管在特定频率下发生阻抗为负的自激震荡现象。

栅极并联电阻,同样可以避免晶体管在特定频率下出现阻抗为负导致的自激振荡。

负反馈可以降低低频功率增益,减少射频晶体管的负阻抗,从而提高功放的稳定性。

通过在漏极并联电阻的方式来降低射频晶体管的功率增益,并减少栅漏之间的反馈电容的密勒效应。

负载牵引放大

在功放中,放大管工作在饱和区。因此其S参数会随着输入信号的变化而变化。

S21会随着输入信号功率的增加而变小,使得线性度变差

要想得到最大的输出功率,其中最关键的就是要通过不断的 loadpull 和 sourcepull 仿真,对源阻抗和负载阻抗进行优化。

自适应偏置

能够让电路的偏置点随输入功率的变化而变化,从而降低直流功耗,提升效率。传统偏置电路采用的是电阻分压原理,使得输出电位控制在理想范围。

将集电Doherty 结构极和基级连接

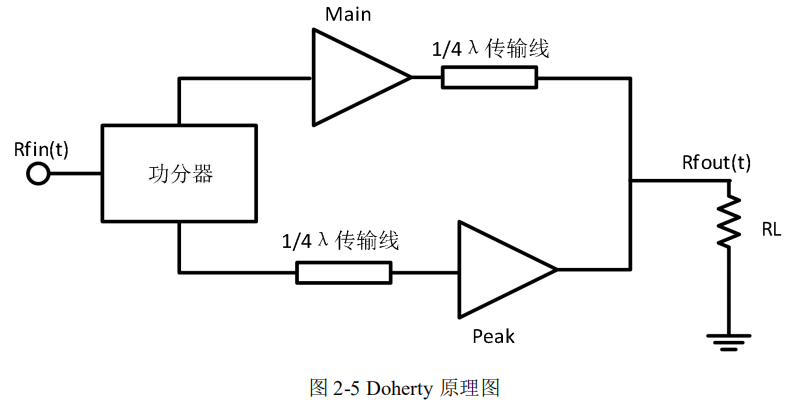

Doherty 结构

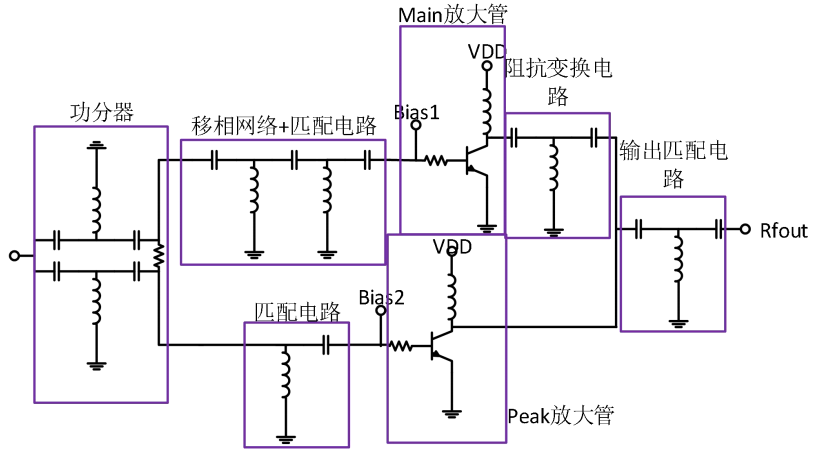

射频信号通过一个功分器,将信号按比例分到两个支路。主放大器和峰值放大器是 Doherty 功率放大器中的两个重要组成部分。主放大器通常通过 50Ω四分之一长传输线来进行负载阻抗调制,并与峰值放大器合成。同样,峰值放大器前也需通过 50Ω四分之一波长传输线进行相位补偿。传统的 Doherty 功率放大器的回退点通常为 6dB。当输入信号功率低于 C 类放大器的阈值时,只有主放大器在工作。随着输入功率的增加,输出功率达到 6dB 的回退点时,主放大器饱和,峰值放大器开始工作。峰值放大器在此时可视为电流源,对主功放负载阻抗进行调制。当两个功放都达到饱和时,主放大器和峰值放大器的输出电流相等,为峰值电流的一半,输出功率也相等,占整个功率放大器输出功率的一半。在 6dB 回退点处,主放大器的效率达到最大值,并一直保持到整个功放达到饱和。

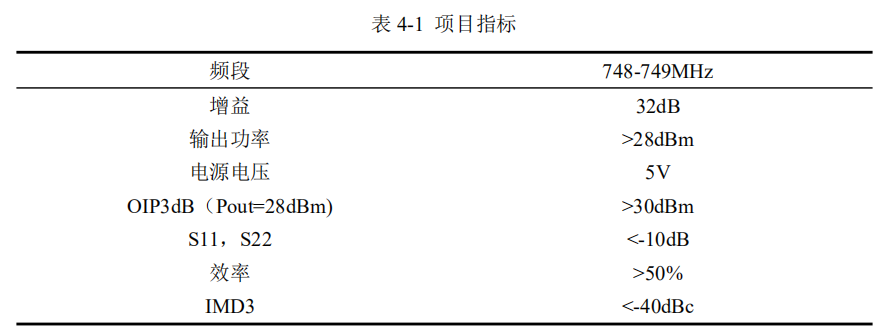

移动通信波段功率放大器设计

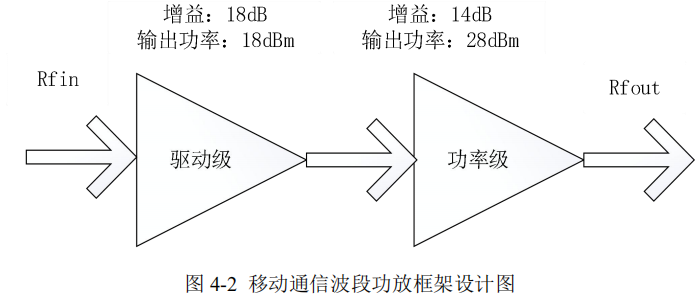

增益要求较高,单级放大器晶体管无法满足该要求,所以用两级电路来进行设计。

晶体管数量也是由要求的,通常晶体管数量会设置成 2 的指数方个,比如 2 个、4 个或者 8 个。

设计流程

搭建好原理图进行 SP 小信号仿真,通过该仿真,可以知道电路最大输出增益是多少,如果不满足,尝试调整偏置电路或者更换电路结构 Loadpull 和 source pull仿真确定合适的源阻抗以及负载阻抗,通常不会只仿真一次 loadpull 和 source pull而是要通过不断迭代,从而达到最优效果。

当迭代到理想的指标时,开始将电路图里面的无源器件及导线换成 EM 仿真后的参数,实际上的电感电容及导线并不是理想的元器件,会有阻抗损耗,根据版图的大小设计合适形状及大小的无源器件画在预设的版图中,不断迭代,直至性能完善。

验证 LVS 以及 DRC。

绘制基板以及测试版。

将完成的芯片版图交付工厂进行流片。

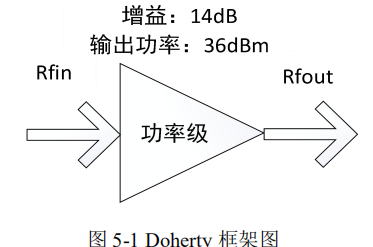

1框架设计

选择单端结构

功率级需要最求最大功率输出,因此增益相较于驱动级会很低。而选取的功率级增益为 13dB,则驱动级至少需要输出 17dBm 的功率。整体设计采用了两极结构。

dBm转换为瓦特(W)

通常来说晶体管面积越大,其输出功率也越大。指标要求输出功率为 28dBm,由于功率级匹配负载会对输出造成一定的损耗,以及为设计留有一定余量,所以假设饱和额定功率为 30dBm。由器件手册给出的数据可知,该工艺的电流密度为0.4mA/um2。偏置电压为 5V,30dBm 的输出功率对应为 1W,22dBm 输出功率对应为 0.16W。

功率放大器中的膝点电压: 对于功率放大器,膝点电压也可以指输出功率从接近零开始急剧增加的电压。这一电压点通常是设计中需要特别关注的,因为它标志着功率放大器进入有效工作区域。

2计算功率级晶体管的面积

3计算负载阻抗

4通过ADS进行IV特性仿真,选择偏置点(功放的工作模式)

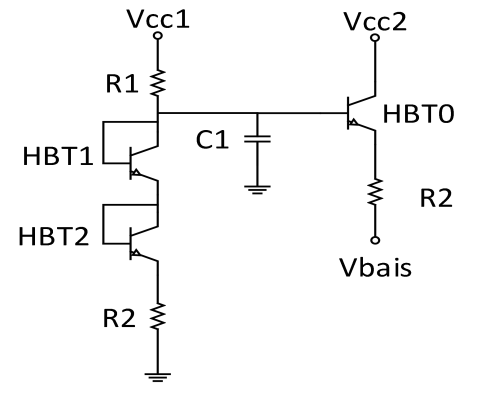

5设计自适应偏置

6输出匹配设计

常见的阻抗匹配有,最大输出功率阻抗匹配,最大效率阻抗匹配以及最大增益阻抗匹配。功率放大器一般以输出最大功率为主要目标,所以在指标选择上偏重于最大输出功率,而最大输出功率的最佳阻抗点并不一定是最大输出增益的最佳阻抗点,因此,需要对指标进行深入研究,对不同指标要求进行取舍。

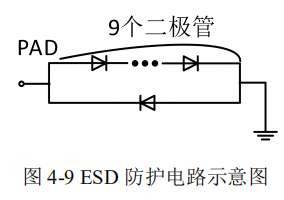

7静电防护网络设计

8谐波抑制电路

串联谐振电路和并联谐振电路

串联谐振电路是一种用于抑制特定频率的电路,其基本原理是在输入信号的频率处形成谐振,使其产生阻抗匹配,从而实现对特定频率的抑制。

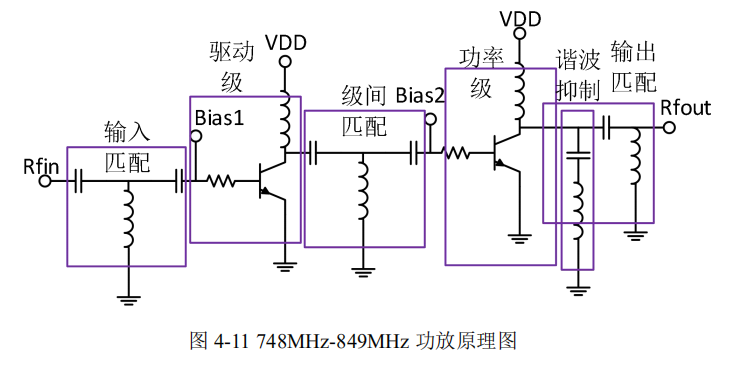

9功放电路

主要由一下几个部分构成,输入匹配部分,驱动级电路,级间匹配电路,功率级电路,谐波抑制电路和输出匹配电路以及偏置电路。

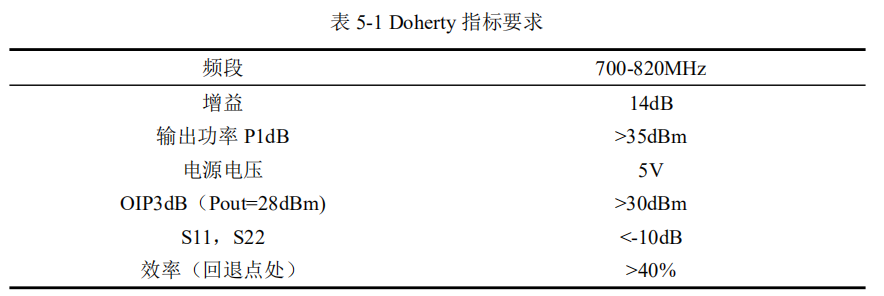

Doherty 功率放大器设计

1项目指标

2整体版图

由于增益要求不高,所以拟采用单级放大。

3晶体管面积估算

4直流仿真以及偏置点选择

5负载阻抗估算

6 SP 以及稳定性仿真

SP 仿真可以看到该偏置点下不同频率下的小信号增益,ads 中内置了判断系统稳定性的因子 mu1 以及 stabfact1,当两个参数都大于 1 时,这证明系统稳定。

7自适应偏置

同上

8 loadpull 最佳阻抗点选取

9匹配电路设计

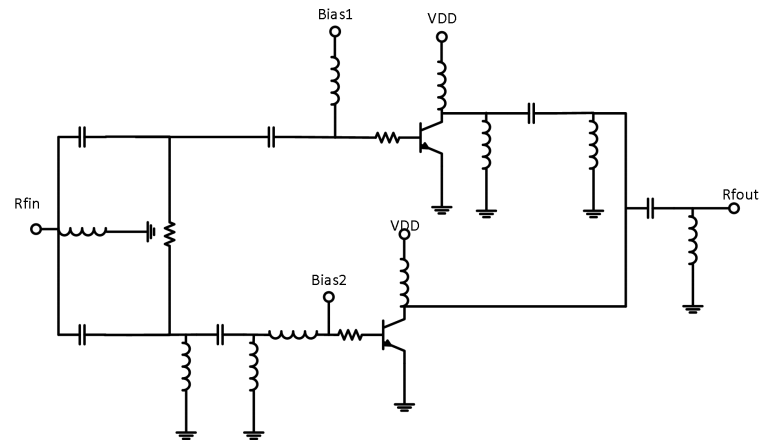

晶体管源端匹配采用常用的 LC 匹配电路结构

10功分器、移相器以及阻抗逆变电路设计

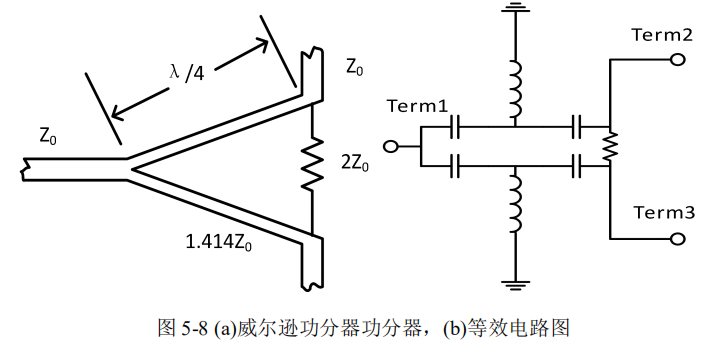

使用电容、电感和电阻组成的网络可以实现功分器的功能。常见的功分器包括 Wilkinson 功分器和双 T 型功分器。

移相器常用于调节信号的相位,常见的移相器包括 T 型或Π型移相网络。

阻抗逆变电路常用于将负载的阻抗与信号源的阻抗匹配,常见的阻抗逆变电路包括 L 型匹配网络和π型匹配网络。

11电路原理图

但实际上,这种原理图中包含了太多的无源器件,画到版图中面积过大,并且由于片上无源器件的低 Q 值,将大大影响电路性能。

改进之后:

将可以优化的无源器件尽量进行优化,采用 LC 集总功分器进行代替 wilkinson 功分器的功能。

总结

第一个设计,匹配电路优化不够完善,后续还可以继续优化其阻抗匹配电路,从而达到更小面积和更好性能。第二个设计,电感数量较多还可以进一步优化,本文的 Doherty 功率放大器设计为了结构简化,设计不同偏置,不同大小晶体管的两个支路最优阻抗相同,实际上两个支路的最优负载阻抗并不完全相同,后续会优化最优负载阻抗点的选取。另外,电路整体的线性度较差,后续会优化peak 支路的设计。